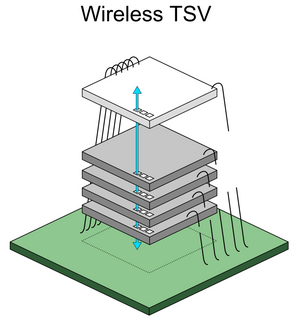

ワイヤレスTSV

ワイヤレスTSV(Wireless Through-Silicon via)とは、電子部品である半導体の実装に関わる3次元積層技術の1つである。従来のワイヤ・ボンディング技術では接続数に限りがあり数十枚の半導体チップを重ねて1つのパッケージ内に納めることは現実的でないが、ワイヤレスTSV技術では、磁界結合による間接的な接続によってSi貫通電極(TSV)と同様に、3次元的に重ねられたチップの上下間で高速信号を受け渡すことが可能になる。

複数のチップが積層され、上下のチップ同士がワイヤレスで磁界結合による通信で結ばれる。図ではチップ同士は上下方向に隙間を空けて描いている。

上のダイがコントローラであり、配線は主にこれに集中される。ダイ同士が同じ位置で密着すると2つ目以下は電源線や接地線がワイヤ・ボンディング出来なくなるので、実際にはチップ同士は互いにずらして重ねる必要がある。

特徴

[編集]本技術はまだ試作段階であるが、すでに以下の特徴はほぼ目処が立っているとされる。

- 低コスト

- 小占有面積

- 低消費電力

- 高速伝送

- 特別なプロセス技術が不要

- 微小化の効果が大

- コイル間は半二重通信[1]

技術

[編集]通信動作

[編集]

チップ(半導体のダイ)の配線層を工夫して作り込まれた小さなコイル同士は、電磁結合によって信号をやり取りする。不要な磁界は配線層による金属の遮蔽板で遮断できる。図ではコイル間は離れて描かれているが、互いの間隔はコイルの直径程度である。

高速通信を低消費電力で行なうには、コイルは小さな方が良く、数十枚のチップを上下に貫通するだけの磁界を生み出せる大きなコイルよりも、小さなコイルをジグザグに配置してリレーを行った方が効率的となる。

図は下向きの通信であるが、同じコイルで送信回路と受信回路が切り替わり、上向きの通信も行なえる。

- コイル

通常のLSIプロセスを用いて微小なコイルを表裏面に磁界が向く方向で作成する。ごく薄[注 1]に削られた複数枚のチップ同士を積層し、上下のチップ間でコイルが対向するように配置する。

- 送信/受信

送信アンプによって片側のコイルにパルス状の信号を加える。キャリアによる変調を加えることなく、送信データをそのまま短いパルスとしてコイルに与えられる。対向した2つのコイルを共振させるのではなく、トランスのように磁界結合によって送信側のコイルのパルス信号は対向する受信側のコイルに伝えられ、受信コイルに生じたパルスは受信アンプによって成形されて、有意なデジタル信号となる。各コイルは送信アンプと受信アンプにつながれ、通信方向が上か下かによって送信と受信の動作が選択される。つまり半二重でのポイント・ツウ・ポイント通信となる。

- 配置と遮蔽

送信コイルと受信コイルの対は上下のチップで対面する必要があり、チップごとの電源線や制御線をワイヤ・ボンディングする領域を確保しながら、単一のチップ・レイアウトで数十枚のチップを上下に接続するための工夫として、重ねたチップ同士を奇数番目のチップと偶数番目のチップで180度向きを変えて少しずらして重ねる。また、2枚ごとに90度方向に少しずらす。こうすることで1枚のチップを間に挟んで送信コイルと受信コイルの対が対向することになる。ただ、このままではコイルの対が上下に多数が連なり、送信方向が一方に向けられなくなるので、送信コイルの下、又は上に金属板による遮蔽板を設ける。この磁界遮蔽金属膜は通常のボンディング・パッドと同じものでよく、コイルの間に挟まれたチップ上に適切に配置する。このような配置を行なうことで、単一のチップ・レイアウトでも上下4枚のチップが1組となって同じように連なり、ジグザグに上方向(アップリンク)や下方向(ダウンリンク)での信号の流れが作られる。

このような複雑な配置を採らずに、多くのチップへ一度に信号を送れるようコイルを一直線に配置する方法も考えられるが、上下方向の最大通信距離がほぼコイルの直径程度であるため、数十枚のチップの厚み分の磁界を作るにはそれだけコイルが大きくなり、コイルの占有面積が拡大してしまう[注 2]。また、コイルの遮蔽をコイル直近に置くと渦電流によって送信出力が削がれるため、コイル対の間に1枚のチップが挟まれる配置をとり、その間のチップに遮蔽板を設けることで有効な送信出力を得ている。

例えば1mm以下で向き合ったコイル間では40GHzの電磁波の近接場になり、コイル間はトランスのように磁界結合によって信号が送られる。コイルの直径程度の近接場から離れた電磁波は距離の3乗に比例して急速に減衰するので、チップ同士のコイルを並べておくだけで縦方向に対向するもの以外の互いの混信は極めて少なくてすむ。直列に対向していても遮蔽板によって結合を遮断できる[1]。

通信速度と消費電力

[編集]コイルであるので周波数特性によって動作速度に物理的限界が生じるが、ごく微小なコイルなので、例えば1対のコイルで10Gビット/秒以上の通信速度が出せる。コイルを含む回路規模が小さく近距離を微小電流で情報をやり取りするので、DDRやXDRのようなチップのインターフェース回路と比べれば1桁以上、消費電力が少なくて済む。動作速度と消費電力は今後の縮小化によってさらに高速・低消費になることが期待される[1]。

実例

[編集]ワイヤレスTSVの試作例では、パケット通信を使用して上下のチップ間での信号のやり取りを行なった。 0.18μmのCMOSプロセスで試作した半導体チップ上には、金属配線層によって直径200μmの微小なコイルや400μmのシールドが作られた。従来だと25本必要だったワイヤ・ボンディングが電源線などの3本で済み、信号は磁界結合によるワイヤレスTSVで送信受信された[1]。

用途・応用

[編集]最先端の高性能デジタル半導体の多くが発熱が大きく放熱の必要性から高集積な積層にはあまり向かないが、フラッシュ・メモリのようなメモリ半導体やアナログとデジタルの混載、プロセッサとメモリの積層、非接触ウエハーテストや実装後のデバッグ・プローブへの使用が考えられる。磁界を発生させるコイルの位置が異なるチップ同士でも、2つのコイルをつなげただけの磁界インターポーザで中間接続することも行なえる[1]。