利用者:加藤勝憲/集積回路の発明

集積回路の発明(しゅうせきかいろのはつめい)の歴史について述べる。最初の平面モノリシック集積回路(IC)チップは1960年に実証された。

集積回路のアイデアの誕生

[編集]ドイツの物理学者でエンジニアのヴェルナー・ヤコビが1949年に初めて集積トランジスタ増幅器を開発し特許を取得したとき、またイギリスの無線技師ジェフリー・ダマーが1952年にモノリシック半導体結晶にさまざまな標準電子部品を集積することを提案したとき、電子回路を単一のデバイスに集積するというアイデアが生まれた。

その1年後、ハーウィック・ジョンソンはICのプロトタイプの特許を申請した。1953年から1957年にかけて、シドニー・ダーリントンと樽井保雄(電気技術研究所)が、複数のトランジスタが共通のアクティブエリアを共有できる同様のチップ設計を提案したが、それらを互いに分離する電気的絶縁はなかった。

アイデアを製品に

[編集]1958年後半に画期的なアイデアが生まれるまで、これらのアイデアは業界では実現できなかった。米国3社の3人が、集積回路の生産を妨げていた3つの根本的な問題を解決したのである。テキサス・インスツルメンツのジャック・キルビーは、集積の原理で特許を取得し、最初のICの試作品を作り、商品化した。キルビーの発明は、モノリシック集積回路ではなく、ハイブリッド集積回路であった[1]。1958年末から1959年初めにかけて、スプレイグ・エレクトリック社のクルト・レホベックは、pn接合絶縁を用いて半導体結晶上の部品を電気的に絶縁する方法を開発した。

最初のモノリシックICチップは、フェアチャイルドセミコンダクターのロバート・ノイスによって発明された[2][3]。彼はICコンポーネントを接続する方法(アルミニウムメタライゼーション)を発明し、ジャン・ヘルニが開発したプレーナプロセス技術に基づく絶縁の改良版を提案した。1960年9月27日、ノイスとヘルニのアイデアを用いて、フェアチャイルドセミコンダクターのジェイ・ラストのグループが最初の動作可能な半導体ICを開発した。キルビーの発明の特許を持っていたテキサス・インスツルメンツは特許戦争を始めたが、1966年にクロスライセンスに関する合意によって決着した。

誰が集積回路を発明したのか?

[編集]誰がICを発明したのか、コンセンサスは得られていない。1960年代のアメリカの新聞は4人の名前を挙げた: 1970年代には、キルビーとノイスにリストが短縮された。キルビーは2000年のノーベル物理学賞を「集積回路の発明の一翼を担った」として受賞した。2000年代に入り、歴史家のレスリー・バーリン[注釈 1]、ボー・ロジェク[注釈 2]、アルジュン・サクセナ[注釈 3]は、複数のIC発明者という考えを復活させ、キルビーの貢献を修正した。現代のICチップは、キルビーのハイブリッドICではなく[1]、ノイスのモノリシックIC[2][3]をベースにしている。

キルビーとノイスは後に、ともにアメリカ国家技術賞を受け、全米発明家殿堂入りをした。

前提条件

[編集]突破口を待っている状態

[編集]

つまり、いくつかの計算装置は、故障やダウンタイムによる損失が期待される利益を上回る複雑なレベルに達していた[6]。ボーイングB-29(1944年就航)には1機あたり300~1000本の真空管と数万個の受動部品が搭載されていた[注釈 4]。先進的なコンピューターでは真空管の数は数千本に達し、ENIAC(1946年)では17,000本以上に達した。部品が増えるたびに装置の信頼性は低下し、トラブルシューティングに要する時間は長くなった[6]。従来のエレクトロニクスは行き詰まりを見せ、電子機器のさらなる発展には部品点数の削減が必要となった。

1947年に最初のトランジスタが発明され、新たな技術革命が期待されるようになった。小説家やジャーナリストは、「インテリジェント・マシン」の出現と生活のあらゆる側面のロボット化が間近に迫っていることを予告した[7]。トランジスタはサイズと消費電力を削減したが、複雑な電子機器の信頼性の問題を解決することはできなかった。それどころか、小型デバイスの中に部品を密集させることは、修理の妨げになった[6]。ディスクリート部品の信頼性は1950年代に理論的限界に達したが、部品間の接続には改善が見られなかった。

集積の考え方

[編集]集積回路の初期の開発は1949年まで遡る。ドイツのエンジニア、ヴェルナー・ヤコビ(シーメンスAG)[8]が、集積回路のような半導体増幅デバイス[9]の特許を申請したとき、共通の基板上に5つのトランジスタを配置し、2つのトランジスタがインピーダンス変換器として「逆さまに」動作する3段増幅器配置を示した。ヤコビは、彼の特許の典型的な産業用途として、小型で安価な補聴器を開示した。彼の特許の直接的な商業利用は報告されていない。

ジェフリー・ダマー

[編集]1952年5月7日、イギリスのラジオ技師ジェフリー・ダマーは、ワシントンで行われた公開演説で統合のアイデアを打ち出した:

ダマーは後に「集積回路の予言者」として有名になったが、発明者ではない。1956年、彼は融液からの成長によってICのプロトタイプを製造したが、彼の研究は、ディスクリートデバイスと比較してICの高コストと劣ったパラメーターのために、英国国防省によって実用的ではないと判断された。

シドニー・ダーリントン、バーナード・オリバー

[編集]1952年5月、シドニー・ダーリントンが、2つまたは3つのトランジスタをさまざまな構成で1つのチップに集積した構造の特許を米国で出願し、1952年10月には、バーナード・オリバーが、電気的に接続された3つの平面トランジスタを1つの半導体結晶上に製造する方法の特許を出願した[12]。

1953年5月21日、ハーウィック・ジョンソンは、様々な電子部品(トランジスタ、抵抗器、集中容量、分布容量)を単一チップ上に形成する方法の特許を出願した。ジョンソンは、集積された1トランジスタ発振器を製造する3つの方法を説明した。いずれも、一端にバイポーラトランジスタを持つ半導体の細い帯を使い、トランジスタの製造方法が異なっていた。ストリップは一連の抵抗として機能し、一括コンデンサは融着によって形成され、逆バイアスpn接合は分布コンデンサとして機能した。ジョンソンは技術的な手順を提示しなかったため、実際のデバイスを製作したかどうかは不明である。1959年、彼の提案の変形がジャック・キルビーによって実現され、特許を取得した[12]。

樽井保雄

[編集]1957年、東京近郊の通産省電気技術研究所の樽井保雄は、ユニポーラ(電界効果トランジスタ)とバイポーラ接合トランジスタを同一チップ上に形成した「四極子」トランジスタを作製した[5]。これらの初期のデバイスは、複数のトランジスタが共通の活性領域を共有できる設計を特徴としていたが、それらを互いに分離する電気的絶縁は存在しなかった[13]。

In 1957, Yasuo Tarui, at MITI's Electrotechnical Laboratory near Tokyo, fabricated a "quadrapole" transistor, a form of unipolar (field-effect transistor) and a bipolar junction transistor on the same chip. These early devices featured designs where several transistors could share a common active area, but there was no electrical isolation to separate them from each other.

Functional electronics

[編集]米国を代表するエレクトロニクス企業(ベル研究所、IBM、RCA、ゼネラル・エレクトリック)は、最小限の受動素子で所定の機能を実現するディスクリート部品の開発に、「数の専制」に対する解決策を求めた。真空管時代、このアプローチは、動作周波数を犠牲にして回路のコストを下げることを可能にした。例えば、1940年代のメモリーセルは、2つの三極管と12個の受動部品で構成され、最大200kHzの周波数で動作した。MHzの応答は、セルあたり2つの5極管と6つのダイオードで達成できる。このセルは、負荷抵抗と入力コンデンサーを備えた1個のサイラトロンで置き換えることができたが、そのような回路の動作周波数は数kHzを超えることはなかった。

The leading US electronics companies (Bell Labs, IBM, RCA and General Electric) sought solution to "the tyranny of numbers" in the development of discrete components that implemented a given function with a minimum number of attached passive elements.[14] During the vacuum tube era, this approach allowed to reduce the cost of a circuit at the expense of its operation frequency. For example, a memory cell of the 1940s consisted of two triodes and a dozen passive components and ran at frequencies up to 200 kHz. A MHz response could be achieved with two pentodes and six diodes per cell. This cell could be replaced by one thyratron with a load resistor and an input capacitor, but the operating frequency of such circuit did not exceed a few kHz.

1952年、ベル研究所のジュエル・ジェイムズ・エバースは、サイラトロンの固体アナログである4層トランジスタ(サイリスタ)を試作した。ウィリアム・ショックレーは、その設計を2端子の「4層ダイオード」(ショックレー・ダイオード)に単純化し、工業生産を試みた。ショックレーは、この新しいデバイスが電話交換機の分極リレーに取って代わることを期待したが、ショックレー・ダイオードの信頼性は受け入れがたいほど低く、彼の会社は衰退していった。

In 1952, Jewell James Ebers from Bell Labs developed a prototype solid-state analog of thyratron – a four-layer transistor, or thyristor.[15] William Shockley simplified its design to a two-terminal "four-layer diode" (Shockley diode) and attempted its industrial production.[16] Shockley hoped that the new device would replace the polarized relay in telephone exchanges;[17] however, the reliability of Shockley diodes was unacceptably low, and his company went into decline.

同時に、サイリスタ回路に関する研究がベル研、IBM、RCAで行われた。イアン・マンロ・ロス(Ian Munro Ross)とL・アーサー・ダサロ(L. Arthur D'Asaro)(ベル研究所)は、サイリスタを使ったメモリセルの実験を行っていた。ジョー・ローグとリック・ディル(IBM)は、単接合トランジスターを使ってカウンターを作っていた。J.トルケル・ウォールマークとハーウィック・ジョンソン(RCA)は、サイリスタと電界効果トランジスタの両方を使用した。ゲルマニウム・サイリスタを使った1955年から1958年の研究は徒労に終わった。1959年夏、キルビー、レホベック、ヘルニの発明が公に知られるようになってから、ダサロがシリコンサイリスタを使った演算シフトレジスタを報告した。このレジスタでは、4個のサイリスタを含む水晶振動子1個が、8個のトランジスタ、26個のダイオード、27個の抵抗に取って代わった。各サイリスタの面積は0.2~0.4mm2で、厚さは約0.1mmだった。回路素子は深い溝をエッチングすることで絶縁された。

At the same time, works on thyristor circuits were carried at Bell Labs, IBM and RCA. Ian Munro Ross and L. Arthur D'Asaro (Bell Labs) experimented with thyristor-based memory cells.[18] Joe Logue and Rick Dill (IBM) were building counters using monojunction transistors. J. Torkel Wallmark and Harwick Johnson (RCA) used both the thyristors and field-effect transistors. The works of 1955–1958 that used germanium thyristors were fruitless. Only in the summer of 1959, after the inventions of Kilby, Lehovec and Hoerni became publicly known, D'Asaro reported an operational shift register based on silicon thyristors. In this register, one crystal containing four thyristors replaced eight transistors, 26 diodes and 27 resistors. The area of each thyristor ranged from 0.2 to 0.4 mm2, with a thickness of about 0.1 mm. The circuit elements were isolated by etching deep grooves.[18]

機能性エレクトロニクスの支持者、半導体時代から見れば、彼らのアプローチは半導体技術の根本的な問題を回避することを可能にした。ショックレー、ロス、ウォールマークの失敗は、このアプローチの誤りを証明した[18]。機能性デバイスの大量生産は、技術的障壁によって妨げられたのである。

Silicon technology

[編集]初期のトランジスタはゲルマニウム製だった。1950年代半ばまでには、より高温で動作するシリコンに取って代わられた。1954年、テキサス・インスツルメンツのゴードン・キッド・ティールが最初のシリコン・トランジスタを製造し、1955年に実用化された。また1954年には、フラーとディッツェンバーガーがシリコン中の拡散に関する基礎的な研究を発表し、ショックレーはこの技術を利用して、不純物濃度のプロファイルを指定したpn接合を形成することを提案した。

Early transistors were made of germanium. By the mid-1950s it was replaced by silicon which could operate at higher temperatures. In 1954, Gordon Kidd Teal from Texas Instruments produced the first silicon transistor, which became commercial in 1955. Also in 1954, Fuller and Dittsenberger published a fundamental study of diffusion in silicon, and Shockley suggested using this technology to form p-n junctions with a given profile of the impurity concentration.[19]

1955年初頭、ベル研究所のカール・フロッシュがシリコンの湿式酸化を開発し、その後2年間、フロッシュ、モル、フラー、ホロニャックがさらに研究を進めた。その後1958年、フロッシュとリンカーン・デリックは、シリコン酸化膜が拡散プロセス中にシリコン表面を保護し、拡散マスキングに使用できることを提案した[6]。この偶然の発見により、ゲルマニウムに対するシリコンの2つ目の基本的な利点が明らかになった。

In early 1955, Carl Frosch from Bell Labs developed wet oxidation of silicon, and in the next two years, Frosch, Moll, Fuller and Holonyak did further research on it.[20] Later in 1958, Frosch and Lincoln Derick proposed that silicon oxide layers could protect silicon surfaces during diffusion processes, and could be used for diffusion masking.[21][22] This accidental discovery revealed the second fundamental advantage of silicon over germanium: contrary to germanium oxides, "wet" silica is a physically strong and chemically inert electrical insulator.

Surface passivation

[編集]表面不動態化とは、半導体の表面を不活性にし、結晶の表面や端に接触する空気や他の物質との相互作用の結果として半導体の特性を変化させないプロセスであり、1957年にベル研究所のモハメド・アタラによって初めて開発された[7][8]。 [9][10]アタラは、熱成長した二酸化ケイ素(SiO2)層の形成によって、シリコン表面の電子状態の濃度が大幅に低下することを発見し[8]、p-n接合の電気的特性を維持し、これらの電気的特性がガス状の周囲環境によって劣化するのを防ぐために、SiO2膜の重要な品質を発見した。彼は、シリコン表面を電気的に安定化させるために酸化シリコン層が使用できることを発見した[6]。彼は、電気が下の導電性シリコンに確実に浸透するように、シリコンウェーハを酸化シリコンの絶縁層でコーティングする新しい半導体デバイス製造方法である表面パッシベーションプロセスを開発した。シリコンウェハーの上に二酸化シリコンの層を成長させることで、アタラは、電気が半導体層に到達するのを妨げる表面状態を克服することができた[7][11]。

Surface passivation, the process by which a semiconductor surface is rendered inert, and does not change semiconductor properties as a result of interaction with air or other materials in contact with the surface or edge of the crystal, was first developed by Mohamed Atalla at Bell Labs,[23][24] in 1957.[25][26][27] Atalla discovered that the formation of a thermally grown silicon dioxide (SiO2) layer greatly reduced the concentration of electronic states at the silicon surface,[24] and discovered the important quality of SiO2 films to preserve the electrical characteristics of p–n junctions and prevent these electrical characteristics from deteriorating by the gaseous ambient environment.[28] He found that silicon oxide layers could be used to electrically stabilize silicon surfaces.[21] He developed the surface passivation process, a new method of semiconductor device fabrication that involves coating a silicon wafer with an insulating layer of silicon oxide so that electricity could reliably penetrate to the conducting silicon below. By growing a layer of silicon dioxide on top of a silicon wafer, Atalla was able to overcome the surface states that prevented electricity from reaching the semiconducting layer.[23][29]

1958年の電気化学学会の会合で、アタラは1957年のメモに基づき、熱酸化によるp-n接合の表面パッシベーションに関する論文を発表し[9]、シリコン表面における二酸化シリコンのパッシベーション効果を実証した[10]。これは、高品質の二酸化シリコン絶縁膜をシリコン表面に熱成長させて、その下のシリコンp-n接合ダイオードやトランジスタを保護できることを示した最初の実証であった。1960年代半ばまでに、シリコン表面を酸化するアタラのプロセスは、事実上すべての集積回路とシリコン・デバイスの製造に使われるようになった[12]。

At a 1958 Electrochemical Society meeting, Atalla presented a paper about the surface passivation of p-n junctions by thermal oxidation, based on his 1957 memos,[25] and demonstrated silicon dioxide's passivating effect on a silicon surface.[27] This was the first demonstration to show that high-quality silicon dioxide insulator films could be grown thermally on the silicon surface to protect the underlying silicon p-n junction diodes and transistors.[30] By the mid-1960s, Atalla's process for oxidized silicon surfaces was used to fabricate virtually all integrated circuits and silicon devices.[31]

Planar process

[編集]

ジャン・ヘルニは、同じ1958年の電気化学学会の会合に出席し、モハメド・アタラの表面不動態化プロセスのプレゼンテーションに興味をそそられた[25]。

ヘルニはある朝、アタラのデバイスについて考えているときに「平面のアイデア」を思いついた。二酸化ケイ素のシリコン表面に対する不動態化効果を利用して、ヘルニは二酸化ケイ素の層で保護されたトランジスタを作ることを提案した[25]。これが、熱酸化物によるアタラ-タネンバウム-シャイブナー・シリコン・トランジスタ不動態化技術の最初の製品実装の成功につながった[32]。

ジャン・ヘルニは、バイポーラ・トランジスタのプレーナー技術を最初に提案した。このプロセスでは、すべてのpn接合が保護層で覆われ、信頼性が大幅に向上するはずだった。しかし当時、この提案は技術的に不可能と考えられていた。n-p-nトランジスタのエミッタ形成にはリンの拡散が必要であり、フロッシュの研究はSiO2がその拡散を妨げないことを示唆していた。1959年3月、ヘルニの元同僚であるチータン・サーは、ヘルニとノイスに、フロッシュの結論に誤りがあることを指摘した。フロッシュは薄い酸化膜を使ったが、1957年から1958年にかけての実験では、厚い酸化膜がリンの拡散を阻止できることを示していたのである。

Jean Hoerni first proposed a planar technology of bipolar transistors. In this process, all the p-n junctions were covered by a protective layer, which should significantly improve reliability. However, at the time, this proposal was considered technically impossible. The formation of the emitter of an n-p-n transistor required diffusion of phosphorus, and the work of Frosch suggested that SiO2 does not block such diffusion.[33] In March 1959, Chih-Tang Sah, a former colleague of Hoerni, pointed Hoerni and Noyce to an error in the conclusions of Frosch. Frosch used a thin oxide layer, whereas the experiments of 1957–1958 showed that a thick layer of oxide can stop the phosphorus diffusion.[34][35]

以上の知識を武器に、ヘルニは1959年3月12日までにプレーナ型トランジスタの最初の試作品を作り、5月1日にはプレーナプロセスの発明として特許を申請した。1960年4月、フェアチャイルドはプレーナ型トランジスタ2N1613を発売し、1960年10月にはメサ型トランジスタ技術を完全に放棄した。1960年代半ばまでに、プレーナプロセスはトランジスタとモノリシック集積回路を製造する主要技術となった。

Armed with the above knowledge, by March 12, 1959, Hoerni made the first prototype of a planar transistor,[36] and on May 1, 1959, filed a patent application for the invention of the planar process.[33] In April 1960, Fairchild launched the planar transistor 2N1613, and by October 1960 completely abandoned the mesa transistor technology.[37] By the mid-1960s, the planar process has become the main technology of producing transistors and monolithic integrated circuits.

Three problems of microelectronics

[編集]集積回路の誕生を妨げたのは、1958年にウォールマークが定式化した3つの根本的な問題であった:

The creation of the integrated circuit was hindered by three fundamental problems, which were formulated by Wallmark in 1958:[38]

- Integration. In 1958, there was no way of forming many different electronic components in one semiconductor crystal. Alloying was not suited to the IC and the latest mesa technology had serious problems with reliability.

- Isolation. There was no technology to electrically isolate components on one semiconductor crystal.

- Connection. There was no effective way to create electrical connections between the components of an IC, except for the extremely expensive and time-consuming connection using gold wires.

こうして、3つの異なる企業が、それぞれの問題に対する重要な特許を保有することになった。スプレイグ・エレクトリック社はICの開発を断念し、テキサス・インスツルメンツ社は不完全な技術に限定し、フェアチャイルド・セミコンダクター社だけがモノリシックICの商業生産に必要なすべての技術を組み合わせた。

It happened so that three different companies held the key patents to each of these problems. Sprague Electric Company decided not to develop ICs, Texas Instruments limited itself to an incomplete set of technologies, and only Fairchild Semiconductor combined all the techniques required for a commercial production of monolithic ICs.

Integration by Jack Kilby

[編集]Kilby's hybrid IC

[編集]1958年5月、第二次世界大戦の退役軍人で経験豊富な無線技師だったジャック・キルビーは、テキサス・インスツルメンツ社で働き始めた[39][40][41] 。当初は具体的な仕事もなく、「小型化」という一般的な方向性の中で、自分で適切なテーマを見つけなければならなかった[40]。彼には、根本的に新しい研究の方向性を見つけるか、軍事用回路の製造に関する数百万ドル規模のプロジェクトに紛れ込むかのどちらかのチャンスがあった[39]。1958年の夏、キルビーは集積化の3つの特徴を定式化した:

- The only thing that a semiconductor company can successfully produce is semiconductors.

- All circuit elements, including resistors and capacitors can be made of a semiconductor.

- All circuit components can be formed on one semiconductor crystal, adding only the interconnections.

1958年8月28日、キルビーはディスクリート部品を使用したICの最初のプロトタイプを組み立て、1チップに実装する承認を得た。彼は、ゲルマニウム(シリコンではない)チップ上に、メサトランジスタ、メサダイオード、p-n接合をベースとしたコンデンサを形成できる技術を入手し、チップのバルク材料を抵抗に使用することができた。25個(5×5)のメサ・トランジスタを製造するためのテキサス・インスツルメンツの標準的なチップの大きさは10×10mmだった。キルビーは、これを10×1.6ミリの5トランジスタ・ストリップに切り分けたが、後に使用したのはそのうちの2つだけだった。9月12日、彼は最初のICプロトタイプを発表した。それは、ジョンソンによる1953年の特許のアイデアと回路を繰り返した、分散型RCフィードバックを備えた1トランジスタ発振器であった。9月19日には、2番目の試作品である2トランジスタ・トリガーを作った。彼は、これらのICについて、ジョンソンの特許を参照しながら、自身の米国特許第 3,138,743号で説明している。

On August 28, 1958, Kilby assembled the first prototype of an IC using discrete components and received approval for implementing it on one chip. He had access to technologies that could form mesa transistors, mesa diodes and capacitors based on p-n junctions on a germanium (but not silicon) chip, and the bulk material of the chip could be used for resistors.[39] The standard Texas Instruments chip for the production of 25 (5×5) mesa transistors was 10×10 mm in size. Kilby cut it into five-transistor 10×1.6 mm strips, but later used not more than two of them.[42][43] On September 12, he presented the first IC prototype,[39] which was a single-transistor oscillator with a distributed RC feedback, repeating the idea and the circuit in the 1953 patent by Johnson.[10] On September 19, he made the second prototype, a two-transistor trigger.[44] He described these ICs, referencing the Johnson's patent, in his アメリカ合衆国特許第 3,138,743号.

1959年2月から5月にかけて、キルビーは一連の出願を行った:アメリカ合衆国特許第 3,072,832号, アメリカ合衆国特許第 3,138,743号, アメリカ合衆国特許第 3,138,744号, アメリカ合衆国特許第 3,115,581号 and アメリカ合衆国特許第 3,261,081号である[45] 。

アルジュン・サクセナによると、肝心の特許3,138,743号の出願日は不確かで、特許とキルビーの著書では1959年2月6日となっているが[46]、連邦特許庁の出願アーカイブでは確認できなかった。キルビー氏は、最初の出願は2月6日に提出され紛失し、(保存されていた)再提出が特許庁に受理されたのは1959年5月6日で、これは特許3,072,832号および3,138,744号の出願と同じ日付であることを示唆した[47]。テキサス・インスツルメンツは1959年3月6日、キルビーによる発明を一般に公開した[48]。

これらの特許はいずれも、分離と相互接続の問題を解決していなかった。部品はチップに溝を切ることで分離され、金線で接続されていた。そのため、これらのICはモノリシック・タイプではなくハイブリッド・タイプだった。しかし、キルビーは、様々な回路素子(能動部品、抵抗器、コンデンサー、さらには小さなインダクタンス)を1つのチップ上に形成できることを実証した。

None of these patents solved the problem of isolation and interconnection – the components were separated by cutting grooves on the chip and connected by gold wires.[42] Thus these ICs were of the hybrid rather than monolithic type.[49] However, Kilby demonstrated that various circuit elements: active components, resistors, capacitors and even small inductances can be formed on one chip.[42]

Commercialization attempts

[編集]

1958年秋、テキサス・インスツルメンツは、キルビーのまだ特許化されていないアイデアを軍用顧客に紹介した[39]。ほとんどの部門が既存の概念にそぐわないとして拒絶したが、米空軍はこの技術が分子エレクトロニクス計画に適合すると判断し[39][51]、キルビーが「機能的電子ブロック」と名付けたICの試作品の生産を発注した[52]。ウェスチングハウスは、テキサス・インスツルメンツの技術にエピタキシャル成長を追加し、1960年1月に米軍から別の注文を受けた[53]。

1961年10月、テキサス・インスツルメンツは空軍のために、キルビーの#587 ICをベースにした300ビットのメモリーを搭載した「分子コンピューター」のデモ機を製作した。ハーヴェイ・クレイゴンは、このコンピューターを100cm3強の体積に収めた。1961年12月、空軍は分子エレクトロニクス計画の中で作られた最初のアナログ・デバイス、無線受信機を受け入れた。これは高価なICを使用したもので、部品点数は10~12点にも満たず、高い確率で故障した。これは、ICは航空宇宙用途でしか正当化できないという意見を生み出した。しかし、航空宇宙産業は、メサ・トランジスタの放射線硬度が低いという理由で、これらのICを拒絶した。

In October 1961, Texas Instruments built for the Air Force a demonstration "molecular computer" with a 300-bit memory based on the #587 ICs of Kilby.[54] Harvey Kreygon packed this computer into a volume of a little over 100 cm3.[54] In December 1961, the Air Force accepted the first analog device created within the molecular electronics program – a radio receiver.[53] It uses costly ICs, which had less than 10–12 components and a high percentage of failed devices. This generated an opinion that ICs can only justify themselves for aerospace applications.[55] However, the aerospace industry rejected those ICs for the low radiation hardness of their mesa transistors.[52]

1960年4月、テキサス・インスツルメンツは、世界初の集積回路としてマルチバイブレーター#502を発表した。同社は、競合他社とは逆に、1個450米ドル、100個以上の場合は300米ドルという価格で、実際に製品を販売すると断言した[52]。しかし、販売が開始されたのは1961年の夏で、価格は発表よりも高かった[56]。#502の回路図には、2個のトランジスタ、4個のダイオード、6個の抵抗、2個のコンデンサーが含まれており、従来のディスクリート回路が繰り返されていた[57]。デバイスは、金属セラミック・ハウジングの中に長さ5mmのSiストリップが2つ入っていた[57]。片方のストリップには入力コンデンサーが、もう片方にはメサ・トランジスターとダイオードが収納され、溝付きの本体は6つの抵抗として使用された。金線が相互接続として機能した[58]。

Isolation by p-n junction

[編集]Solution by Kurt Lehovec

[編集]1958年末、スプレイグ・エレクトリック社に勤めていた科学者カート・レホベックは、プリンストン大学で開催されたセミナーに出席し、そこでウォールマークがマイクロエレクトロニクスの基本的な問題についてのビジョンを説明した。マサチューセッツに戻る途中、レホベックはpn接合を使った絶縁問題の簡単な解決策を見つけた:[59]

p-n接合は、特に、いわゆるブロッキング方向にバイアスされた場合、またはバイアスが印加されていない場合に、電流に対して高いインピーダンスを有することはよく知られている。従って、同一スライス上に組み立てられた2つの部品間の電気絶縁は、当該部品が組み立てられた2つの半導体領域間に十分な数のpn接合を直列に配置することにより、任意の所望の程度を達成することができる。ほとんどの回路では、1~3個の接合で十分である。

レホベックは、スプラグで利用可能だったトランジスタの製造技術を使って、彼のアイデアをテストした。彼のデバイスは、2.2×0.5×0.1mmの大きさの線状構造で、p-n接合によって孤立したn型セル(将来のトランジスタのベース)に分割されていた。層と遷移は、融液からの成長によって形成された。導電性のタイプは、結晶の引き上げ速度によって決定された。インジウムリッチなp型層は低速で形成され、ヒ素リッチなn型層は高速で形成された。トランジスタのコレクターとエミッターは、インジウム・ビーズを溶接することによって作られた。電気的接続はすべて手作業で、金線を使用した。

スプラグの経営陣はレホヴェックの発明に関心を示さなかった。それにもかかわらず、1959年4月22日、彼は自費で特許を申請し、その後2年間米国を離れた。この離脱により、ゴードン・ムーアはレホベックを集積回路の発明者と見なすべきではないと結論づけた。

Solution by Robert Noyce

[編集]

1959年1月14日、ジャン・ヘルニは、フェアチャイルドセミコンダクターのロバート・ノイスと弁理士ジョン・ラルザに、最新版のプレーナプロセスを紹介した。この時のヘルニのメモが、1959年5月に出願されたプレーナプロセスの発明に関する特許出願の基礎となった、 そして、米国特許第 3,025,589号(プレーナプロセス)および米国特許第 3,064,167号(プレーナトランジスタ)に実装された。1959年1月20日、フェアチャイルドの経営陣は、ロケット「アトラス」に搭載されるコンピュータの開発者であるエドワード・キオンジアンと会談し、彼のコンピュータ用のハイブリッドデジタルICの共同開発について話し合った。このような出来事が、ロバート・ノイスを統合という考えに立ち戻らせたのだろう。

January 14, 1959, Jean Hoerni introduced his latest version of the planar process to Robert Noyce and a patent attorney John Rallza at Fairchild Semiconductor.[60][61] A memo of this event by Hoerni was the basis of a patent application for the invention of a planar process, filed in May 1959, and implemented in アメリカ合衆国特許第 3,025,589号 (the planar process) and アメリカ合衆国特許第 3,064,167号 (the planar transistor).[62] On January 20, 1959, Fairchild managers met with Edward Keonjian, the developer of the onboard computer for the rocket "Atlas", to discuss the joint development of hybrid digital ICs for his computer.[63] These events probably led Robert Noyce to return to the idea of integration.[64]

1959年1月23日、ノイスは、ヘルニのプレーナプロセスをベースに、キルビーとレホベックのアイデアを基本的に再発明したプレーナ集積回路のビジョンを文書化した。ノイスは1976年に、1959年1月の時点ではレホベックの研究を知らなかったと主張している。

On January 23, 1959, Noyce documented his vision of the planar integrated circuit, essentially re-inventing the ideas of Kilby and Lehovec on the base of the Hoerni's planar process.[65] Noyce claimed in 1976 that in January 1959 he did not know about the work of Lehovec.

一例として、ノイスはキオンジアンと議論したインテグレーターについて述べた[66]。その仮想デバイスのトランジスタ、ダイオード、抵抗は、pn接合によって互いに絶縁されていたが、レホベックによる解決策とは異なる方法であった。ノイスは、ICの製造プロセスを次のように考えた。まず、酸化膜でパッシベーションされた高抵抗の固有(アンドープ)シリコンのチップから始める。最初のフォトリソグラフィ工程では、計画されたデバイスに対応する窓を開け、不純物を拡散させてチップの厚さ全体に低抵抗の「ウェル」を形成する。その後、従来のプレーナー・デバイスがその井戸の中に形成される【ここに注32が入る】

。レホヴェックによる解決策とは逆に、このアプローチでは2次元構造が作られ、チップ上に無制限にデバイスを配置できる可能性がある。

アイデアを練った後、ノイスは会社の急用で数ヶ月間そのアイデアを棚上げにし、1959年3月になってようやくそのアイデアに戻った[67]。特許出願の準備に6ヵ月を要したが、米国特許庁はすでにレホベックの出願を受理していたため[68]、この出願は却下された。ノイスは出願を修正し、1964年にアメリカ合衆国特許第 3,150,299号 とアメリカ合衆国特許第 3,117,260号を取得した[69]。

Invention of metallization

[編集]1959年初頭、ノイスはもう一つの重要な問題、ICの大量生産を妨げていた相互接続の問題を解決した[70]。8人の反逆者の同僚によると、彼のアイデアは自明のことだったという。もちろん、パッシベーション酸化膜はチップとメタライゼーション層の間に自然なバリアを形成する[71]。キルビーとノイスの同僚だったターナー・ヘイスティ(Turner Hasty)によると、ノイスはフェアチャイルドのマイクロエレクトロニクス特許を、1951年から1952年にかけてトランジスタ技術を発表したベル研究所と同じように、幅広い企業が利用できるようにすることを計画していた。

ノイスは1959年7月30日に出願し、1961年4月25日にアメリカ合衆国特許第 2,981,877号を取得した。特許によると、この発明は、メタライゼーション層とチップ(コンタクトウインドウ部分を除く)を隔てる酸化膜を温存し、金属層を酸化膜に強固に密着するように蒸着することにあった。成膜方法はまだ知られておらず、ノイスによる提案には、マスクを通してアルミニウムを真空蒸着し、連続層を成膜した後、フォトリソグラフィーを行い、余分な金属をエッチングで除去する方法が含まれていた。サクセナによれば、ノイスによる特許は、その欠点はあるにせよ、現代のIC技術の基本を正確に反映しているという[72]。

特許の中で、キルビーはメタライゼーション層の使用にも言及している。しかし、キルビーは二酸化ケイ素の代わりに異なる金属(アルミニウム、銅、アンチモンドープ金)と一酸化ケイ素の厚いコーティング層を好んだ。これらのアイデアはICの製造には採用されなかった[73]。

First monolithic integrated circuits

[編集]

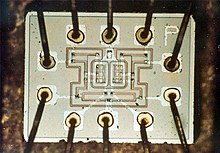

1959年8月、ノイスはフェアチャイルド社に集積回路を開発するグループを結成した。1960年5月26日、ジェイ・ラストが率いるこのグループは、最初のプレーナー集積回路を完成させた。このプロトタイプはモノリシックではなく、ラストの特許によれば、2組のトランジスタはチップに溝を切ることで分離されていた。初期の生産段階では、ヘルニのプレーナープロセスが繰り返された。その後、厚さ80ミクロンの結晶を下向きにガラス基板に接着し、裏面にフォトリソグラフィーを施した。ディープエッチングで表面まで溝を作った。その後、裏面をエポキシ樹脂で覆い、チップをガラス基板から切り離した。

In August 1959, Noyce formed at Fairchild a group to develop integrated circuits.[74] On May 26, 1960, this group, led by Jay Last, produced the first planar integrated circuit. This prototype was not monolithic – two pairs of its transistors were isolated by cutting a groove on the chip, according to the patent by Last.[75] The initial production stages repeated the Hoerni's planar process. Then the 80-micron-thick crystal was glued, face down, to the glass substrate, and additional photolithography was carried on the back surface. Deep etching created a groove down to the front surface. Then the back surface was covered with an epoxy resin, and the chip was separated from the glass substrate.

1960年8月、ラストはノイスが提案したp-n接合による絶縁を用いた2番目の試作品に取りかかった。ロバート・ノーマンは、4つのトランジスタと5つの抵抗によるトリガー回路を開発し、イシー・ハースとライオネル・カットナーは、絶縁領域を形成するためのホウ素拡散プロセスを開発した。最初の動作デバイスは1960年9月27日にテストされ、これが最初のプレーナーでモノリシックな集積回路となった。

In August 1960, Last started working on the second prototype, using the isolation by p-n junction proposed by Noyce. Robert Norman developed a trigger circuit on four transistors and five resistors, whereas Isy Haas and Lionel Kattner developed the process of boron diffusion to form the insulating regions. The first operational device was tested on September 27, 1960 – this was the first planar and monolithic integrated circuit.

フェアチャイルドセミコンダクターはこの仕事の重要性に気づいていなかった。マーケティング担当副社長は、ラストが会社の資源を無駄遣いしていると考え、プロジェクトを中止すべきだと考えた。1961年1月、ラスト、ヘルニ、そして 「裏切り者8人衆 」のクライナー、ロバーツはフェアチャイルドを去り、アメルコに向かった。デビッド・アリソン、ライオネル・カトナー、その他数名の技術者はフェアチャイルド社を去り、直接の競合会社であるシグネティックス社を設立した。

Fairchild Semiconductor did not realize the importance of this work. Vice president of marketing believed that Last was wasting the company resources and that the project should be terminated.[76] In January 1961, Last, Hoerni and their colleagues from the "traitorous eight" Kleiner and Roberts left Fairchild and headed Amelco. David Allison, Lionel Kattner and some other technologists left Fairchild to establish a direct competitor, the company Signetics.[77]

最初の集積回路の発注は、論理素子64個、1個1000ドルで、パッケージング案のサンプルは1960年にMITに、64個のテキサス・インスツルメンツ集積回路は1962年に納入された[14]。

The first integrated circuit purchase order was for 64 logic elements at $1000 each, with samples of proposed packaging delivered to MIT in 1960 and the 64 Texas Instruments integrated circuits in 1962.

主要な科学者やエンジニアが去ったにもかかわらず、1961年3月、フェアチャイルドは「マイクロロジック」と名付けた初の商用ICシリーズを発表し、その後1年をかけてロジックICファミリーを作り上げた。その頃、ICはすでに競合他社によって製造されていた。テキサス・インスツルメンツはキルビーによるIC設計を放棄し、宇宙衛星用の一連のプレーナーICを受注し、その後LGM-30ミニットマン弾道ミサイル用のICを受注した。

Despite the departure of their leading scientists and engineers, in March 1961 Fairchild announced their first commercial IC series, named "Micrologic", and then spent a year on creating a family of logic ICs. By that time ICs were already produced by their competitors. Texas Instruments abandoned the IC designs by Kilby and received a contract for a series of planar ICs for space satellites, and then for the LGM-30 Minuteman ballistic missiles.

NASAのアポロ計画は、1961年から1965年にかけて、集積回路の単独で最大の消費者だった[14]。

NASA's Apollo Program was the largest single consumer of integrated circuits between 1961 and 1965.

アポロ宇宙船に搭載されたコンピューターのICはフェアチャイルド社によって設計されたが、そのほとんどはレイセオン社とフィルコフォード社によって製造された。これらのコンピューターにはそれぞれ約5,000個の標準ロジックICが搭載され、その製造過程でICの価格は1,000米ドルから20~30米ドルに下がった。このようにして、NASAと国防総省は非軍事用IC市場の基盤を整えたのである。

Whereas the ICs for the onboard computers of the Apollo spacecraft were designed by Fairchild, most of them were produced by Raytheon and Philco Ford.[78] Each of these computers contained about 5,000 standard logic ICs,[78] and during their manufacture, the price for an IC dropped from US$1,000 to US$20–30. In this way, NASA and the Pentagon prepared the ground for the non-military IC market.[79]

アポロ誘導コンピュータのすべての論理ICを含む最初のモノリシック集積回路は、3入力抵抗トランジスタ論理NORゲートだった。

The first monolithic integrated circuits, including all the logic ICs in the Apollo Guidance Computer, were 3-input resistor-transistor logic NOR gates.

フェアチャイルドとテキサス・インスツルメンツによる最初のICの抵抗トランジスタ・ロジックは電磁干渉に弱かったため、1964年に両社はダイオード・トランジスタ・ロジックに置き換えた[91]。シグネティックスは1962年にダイオード・トランジスタ・ファミリーのユーティロジックをリリースしたが、生産の拡大とともにフェアチャイルドとテキサス・インスツルメンツに遅れをとった。1961年から1965年のIC販売数ではフェアチャイルドがトップであったが、売上ではテキサス・インスツルメンツが上回っていた: 1964年にはIC市場の32%を占めたのに対し、フェアチャイルドは18%だった。

TTL integrated circuits

[編集]上記のロジックICは、技術プロセスによってサイズや構成が定義された標準的な部品から作られており、1つのIC上のダイオードとトランジスタはすべて同じタイプだった。異なるタイプのトランジスタの使用は、1961年から1962年にかけてシルバニアのトム・ロングによって初めて提案された。

The above logic ICs were built from standard components, with sizes and configurations defined by the technological process, and all the diodes and transistors on one IC were of the same type.[80] The use of different transistor types was first proposed by Tom Long at Sylvania during 1961–1962.

1961年、トランジスタ・トランジスタ・ロジック(TTL)はジェイムズ・L・ブイによって発明された[15]。1962年後半、シルバニアはトランジスタ・トランジスタ・ロジック(TTL)ICの最初のファミリーを発売し、商業的成功を収めた。フェアチャイルドのボブ・ウィドラーは1964年から1965年にかけて、アナログIC(オペアンプ)でも同様の躍進を遂げた。TTLは、1970年代から1980年代初頭にかけて支配的なIC技術となった[15]。

In 1961, transistor–transistor logic (TTL) was invented by James L. Buie.[81] In late 1962, Sylvania launched the first family of transistor-transistor logic (TTL) ICs, which became a commercial success.[82] Bob Widlar from Fairchild made a similar breakthrough in 1964–1965 in analog ICs (operational amplifiers).[83] TTL became the dominant IC technology during the 1970s to early 1980s.[81]

MOS integrated circuit

[編集]MOSトランジスタとしても知られるMOSFET(金属-酸化膜-シリコン電界効果トランジスタ)は、1959年にベル研究所のモハメド・アタラとダウォン・カーンによって発明された[84]。MOSFETは高密度集積回路の製造を可能にした[85]。ほぼすべての現代のICは、MOSFET(金属-酸化膜-シリコン電界効果トランジスタ)から構築されたMOS(金属-酸化膜-半導体)集積回路である[86]。実験的に製造された最も初期のMOS ICは、1962年にRCA社のフレッド・ハイマンとスティーブン・ホフスタインが製造した16トランジスタのチップであった[87]。1962年、RCA社のフレッド・ハイマン(Fred Heiman)とスティーブン・ホフスタイン(Steven Hofstein)によって製造された16トランジスタのチップが、最も早く製造された実験的MOS ICである[88]。その後、ゼネラル・マイクロエレクトロニクスは1964年に、ロバート・ノーマンによって開発された120トランジスタのシフトレジスタを搭載した、初の商用MOS集積回路を発表した[89]。MOSFETはそれ以来、現代のICで最も重要なデバイス部品となっている[90]。

Patent wars of 1962–1966

[編集]1959年から1961年にかけて、テキサス・インスツルメンツとウェスティングハウスが航空「分子エレクトロニクス」の開発に並行して取り組んでいた頃、両社の競争は友好的な性格を帯びていた。1962年、テキサス・インスツルメンツは自社特許の実在・架空の侵害者を熱心に追及し始め、「ダラスの法律事務所」[91]や「半導体のカウボーイ」[92]というニックネームが付けられると、状況は一変した。テキサスインスツルメンツ以外の企業もこの例に倣った[91]。この例は、他のいくつかの企業も追随した。それでも、IC産業は特許紛争をものともせず発展を続けた[93]。1960年代初頭、米国控訴裁判所は、ノイスが熱酸化膜とp–n接合分離技術に基づくモノリシック集積回路チップの発明者であるとの判決を下した[94]。

- Texas Instruments v. Westinghouse

- これらの企業がプレーナープロセスを採用していた1962年から1963年にかけて、ウェスチングハウスの技術者、林鴻章はラテラルトランジスタを発明した。通常のプレーナー・プロセスでは、すべてのトランジスタの導電型は同じで、通常はn-p-n型であったが、林の発明により、1つのチップ上にn-p-n型とp-n-p型のトランジスタを作ることができるようになった[95]。テキサス・インスツルメンツ社が見込んでいた軍からの発注はウェスティングハウス社に渡った。TIは裁判を起こしたが、示談で解決した[96]。

- Texas Instruments v. Sprague

- 1962年4月10日、レホベックはpn接合による絶縁の特許を取得した。テキサス・インスツルメンツ社は、絶縁の問題はキルビーが先に出願した特許で解決済みであると主張し、直ちに裁判を起こした。スプレイグの創業者であるロバート・スプレイグは、この訴訟は絶望的と考え、特許権を放棄しようとしていたが、レホベックに説得された。4年後、テキサス・インスツルメンツはダラスで、キルビーの発明の実演と専門家による宣誓証言が行われる仲裁審問を開催した。しかし、レホベックは、キルビーが部品の分離について言及していないことを決定的に証明した。1966年4月、ようやく彼の分離特許の優先権が認められた[97]。

- Raytheon v. Fairchild

- 1962年5月20日、すでにフェアチャイルド社を退社していたジャン・ヘルニが、プレーナー技術に関する最初の特許を取得した。レイセオンは、ヘルニがジュール・アンドリュースとレイセオンが持っていた特許を繰り返したと考え、裁判を起こした。フォトリソグラフィ、拡散、エッチングの各プロセスは類似しているように見えたが、アンドリュースのアプローチには根本的な欠陥があった。逆に、ヘルニのプロセスでは、「汚れた」酸化膜はそのままだった。レイセオンはその主張を撤回し、フェアチャイルド社からライセンスを取得した[62]。

- Hughes v. Fairchild

- ヒューズ・エアクラフト社は、自社の研究者が先にヘルニのプロセスを開発したとしてフェアチャイルド社を訴えた。フェアチャイルドの弁護士によると、この訴訟には根拠がなかったが、数年かかる可能性があり、その間フェアチャイルドはヘルニのプロセスのライセンスを売ることができなかった。そのため、フェアチャイルドはヒューズと法廷外で和解することを選択した。ヒューズはヘルニの特許の17点のうちの1点の権利を取得し、フェアチャイルドの将来のライセンス収入のわずかな割合と交換した[62]。

- Texas Instruments v. Fairchild

- 法廷闘争においてテキサス・インスツルメンツは、最大かつ最も技術的に進んだ競合相手であるフェアチャイルド・セミコンダクターに焦点を当てた。彼らの訴訟はフェアチャイルドの生産ではなく、彼らの技術のライセンス販売を妨げた。1965年までに、フェアチャイルドのプレーナー技術は業界標準となったが、ヘルニとノイスの特許のライセンスは10社以下のメーカーしか購入できず、ライセンス外の生産を追求する仕組みはなかった[93]。同様に、キルビーの主要特許はテキサス・インスツルメンツに何の収入ももたらさなかった。1964年、特許調停はテキサス・インスツルメンツに、係争特許の5つの重要条項のうち4つの権利を与えたが[98]、両社はこの決定を不服として控訴した[99]。1966年4月にスプレイグ社との係争でテキサス・インスツルメンツ社が敗れなければ、訴訟は何年も続く可能性があった。テキサス・インスツルメンツ社は、主要なIC特許の全セットの優先権を主張できないことを理解し、特許戦争への関心を失った[100]。1966年夏[99]、テキサス・インスツルメンツとフェアチャイルドは特許の相互承認と主要特許のクロスライセンスに合意し、1967年にはスプレイグが加わった[100]。

- Japan v. Fairchild

- 1960年代初頭、フェアチャイルドとテキサス・インスツルメンツの両社は日本でIC生産を行おうとしたが、通産省の反対を受けた。1962年、通産省はフェアチャイルドがすでに日本で購入した工場へのさらなる投資を禁止し、ノイスはNECという企業を通じて日本市場に参入しようとした。1963年、NECの経営陣はフェアチャイルドに日本にとって極めて有利なライセンス条件を突きつけ、日本市場でのフェアチャイルドの販売を強く制限した。ノイスは、NECの社長がフェアチャイルドの取引を妨害した通産省の委員会の委員長も務めていたことを、取引成立後に初めて知った。

- In the early 1960s, both Fairchild and Texas Instruments tried to set up IC production in Japan, but were opposed by the Japan Ministry of International Trade and Industry (MITI). In 1962, MITI banned Fairchild from further investments in the factory that they already purchased in Japan, and Noyce tried to enter the Japanese market through the corporation NEC.[101] In 1963, the management of NEC pushed Fairchild to extremely advantageous for Japan licensing terms, strongly limiting the Fairchild sales in the Japanese market.[102] Only after concluding the deal Noyce learned that the president of NEC also chaired the MITI committee that blocked the Fairchild deals.[103]

- Japan v. Texas Instruments

- 1963年、テキサス・インスツルメンツは、NECやソニーとの苦い経験にもかかわらず、日本での生産を確立しようとした[104]。1965年、テキサス・インスツルメンツは報復として、特許を侵害する電子機器の輸入を禁止すると脅した。この措置は1966年にソニー、1967年にシャープに打撃を与え[105]、通産省はテキサス・インスツルメンツに対抗する日本のパートナーを密かに探すようになった。通産省はテキサス・インスツルメンツと三菱(シャープのオーナー)との交渉を妨害し、「日本産業の未来のために」テキサス・インスツルメンツと取引するよう盛田昭夫を説得した[106]。1967年から1968年にかけての協定は、ソニーの株をアメリカ側に保証する秘密規約があったにもかかわらず、テキサス・インスツルメンツにとって極めて不利なものであった[107]。約30年間、日本企業はテキサス・インスツルメンツにロイヤリティーを支払うことなくICを生産し、1989年になってようやく日本の裁判所がキルビーによる発明の特許権を認めた。その結果、1990年代には、日本のICメーカーはすべて、30年前の特許の対価を支払うか、クロスライセンス契約を結ばなければならなくなった。1993年、テキサス・インスツルメンツは、主に日本企業から5億2000万米ドルのライセンス料を得た。

Historiography of the invention

[編集]Two inventors: Kilby and Noyce

[編集]1960年代の特許戦争中、米国のマスコミや専門家たちは、IC発明者の数がかなり多いことを認識していた。起業家の黄金時代』という本には、4人の名前が挙げられている: キルビー、レホベック、ノイス、ヘルニである[108]。ソラブ・ガンディは、「Theory and Practice of Microelectronics」(1968年)の中で、レホベックとヘルニの特許は1950年代の半導体技術の頂点であり、ICの大量生産への道を開いたと書いている。

1966年10月、キルビーとノイスは、「集積回路の開発に対する重要かつ本質的な貢献」に対して、フランクリン協会からバランタイン・メダルを授与された[99]。この出来事は、2人の発明家というアイデアを生み出すきっかけとなった。キルビーのノミネートは、彼のプロトタイプを「本物の」半導体ICと認めなかった同時代の人々から批判を浴びた。技術者コミュニティは、ムーア、ヘルニ、その他の主要な発明者の役割をよく知っていたのに対し、ノイスは発明当時フェアチャイルドのCEOであり、最初のICの創造には直接参加していなかった。ノイス自身、「私は生産上の問題を解決しようとしていた[99]。集積回路を作ろうとしていたわけではない」とノイス自身も認めている[109]。

レスリー・バーリンによれば、ノイスが「集積回路の父」となったのは、特許戦争のためだった。テキサス・インスツルメンツは、自分たちが異議申し立てをした特許に彼の名前があったため、彼の名前を選び、それによってフェアチャイルドのすべての開発作業の唯一の代表者として彼を「任命」した[110]。その結果、フェアチャイルドは会社を守るためにあらゆる資源を動員し、ノイスを優先したのである[111]。キルビーがテキサス・インスツルメンツの広報活動に個人的に関与していたのに対し、ノイスは公の場から遠ざかり、ゴードン・ムーアが代役を務めた[112]。

1970年代半ばまでに、2人の発明者のバージョンは広く受け入れられるようになり、1976年から1978年にかけて専門誌でキルビーとレホベックが論争を繰り広げたが、状況は変わらなかった。ヘルニ、ラスト、レホベックはマイナーな存在とみなされ、大企業の代表者でもなく、公的な優先順位の高い議論には熱心ではなかった[113]。

1980年代の科学論文では、IC発明の歴史はしばしば次のように紹介されていた。

In scientific articles of the 1980s, the history of IC invention was often presented as follows

フェアチャイルド在籍中に、ノイスは集積回路を開発した。同じコンセプトは、その数ヵ月前にダラスのテキサス・インスツルメンツのジャック・キルビーによって発明されていた。1959年7月、ノイスは自身の考案した集積回路の特許を申請した。テキサス・インスツルメンツは、ノイスとフェアチャイルドを相手取って特許妨害訴訟を起こし、この訴訟は何年も長引いた。今日、ノイスとキルビーは、通常、集積回路の共同発明者とみなされているが、キルビーは発明者として発明家の殿堂入りを果たしている。いずれにせよ、ノイスは集積回路を改良し、マイクロエレクトロニクスの分野で多くの応用を可能にしたと評価されている。[114]

1984年、トーマス・リードは『The Chip: How Two Americans Invented the Microchip and Launched a Revolution(ザ・チップ:いかにして2人のアメリカ人がマイクロチップを発明し、革命を起こしたか)』で、2人の発明者説をさらに支持した。この本は2008年まで再版された。ニューヨーク・タイムズ』紙のロバート・ライトは、リードが発明に関与した脇役について長々と記述しているにもかかわらず、レホベックとラストの貢献には触れておらず、ジャン・ヘルニもノイスに相談した理論家としてしか登場していないと批判した[115]:76。

ポール・セルッツィ(Paul Ceruzzi)も『A History of Modern Computing』(2003年)の中で、この2人の発明家のストーリーを繰り返し、「最初はマイクロロジック(Micrologic)と呼ばれ、その後フェアチャイルド(Fairchild)によって集積回路(Integrated Circuit)と呼ばれた彼らの発明は、(1950年代の軍事計画によって求められた小型化の)この道に沿ったもう一つのステップに過ぎなかった」と述べている[116]。セルッツィは、一般的な文献の意見に言及し、ICの大量生産への道を開いたが、IC発明者のリストには含まれていないヘルニのプレーナプロセスを使用するというノイスの決定を提唱した[117]。セルッツィはIC部品の分離の発明を取り上げなかった。Paul Ceruzzi

2000年、ノーベル委員会は「集積回路の発明の一翼を担った」キルビーにノーベル物理学賞を授与した。ノイスは1990年に死去したため、ノミネートされることはなかった。生前、ノーベル賞の見通しについて尋ねられた際、彼は「エンジニアリングや実際の仕事にはノーベル賞は与えられない」と答えている[118]。ノーベル賞の推薦手続きには守秘義務があるため、他のIC発明者が候補に挙がっていたかどうかは不明である。サクセナは、キルビーの貢献は基礎科学ではなく純粋な工学であり、したがって彼のノミネートはアルフレッド・ノーベルの意志に反すると主張した[119]。

The two-inventor version persisted through the 2010s. Its variation puts Kilby in front, and considers Noyce as an engineer who improved the Kilby's invention. Fred Kaplan in his popular book "1959: The Year Everything Changed" (2010) spends eight pages on the IC invention and assigns it to Kilby,[120] mentioning Noyce only in a footnote[121] and neglecting Hoerni and Last.

Revision of the canonical version

[編集]In the late 1990s and 2000s a series of books presented the IC invention beyond the simplified two-person story:

In 1998, Michael Riordan and Lillian Hoddson described in detail the events leading to the invention of Kilby in their book "Crystal Fire: The Birth of the Information Age". However, they stopped on that invention.[122]

Leslie Berlin in her biography of Robert Noyce (2005) included the events unfolding at Fairchild and critically evaluated the contribution of Kilby. According to Berlin, the connecting wires "precluded the device from being manufactured in any quantity" which "Kilby was well aware" of.[123][70]

In 2007, Bo Lojek opposed the two-inventor version;[124] he described the contributions of Hoerni and Last, and criticized Kilby.[125]

In 2009, Saxena described the work of Lehovec, and Hoerni. He also played down the role of Kilby and Noyce.[126]

関連項目

[編集]脚注・参考文献

[編集]注釈

[編集]- ^ Leslie Berlin is a professional historian, head of the Stanford University program on the history of the Silicon Valley, author of the biography of Robert Noyce, and a Smithsonian Institution advisor.

- ^ Bo Lojek is a solid-state physicist specializing in diffusion in silicon; he wrote a book on the history of semiconductor industry.[4]

- ^ Arjun Saxena is an Indian-American physicist who studied semiconductors since the 1960s; he wrote a book on the history of IC invention.[5]

- ^ In his Nobel Prize lecture, Kilby (Kilby, 2000, p. 474) said that "Even the B-29, probably the most complex equipment used in the war, had only around 300 vacuum tubes", but in a 1976 article (Kilby 1976, p. 648) he mentioned a number of almost a thousand, which agrees with Berry, C. (1993). Inventing the future: how science and technology transform our world. Brassey's. p. 8. ISBN 9780028810294

脚注

[編集]- ^ a b Saxena 2009, p. 140.

- ^ a b “1959: Practical Monolithic Integrated Circuit Concept Patented”. Computer History Museum. 13 August 2019閲覧。

- ^ a b “Integrated circuits”. NASA. 13 August 2019閲覧。

- ^ Lojek 2007.

- ^ Saxena 2009.

- ^ a b c Kaplan 2010, p. 78.

- ^ Kaplan 2010, p. 77.

- ^ “Integrated circuits help Invention”. Integratedcircuithelp.com. 2012年10月11日時点のオリジナルよりアーカイブ。2012年8月13日閲覧。

- ^ DE 833366 W. Jacobi/SIEMENS AG: „Halbleiterverstärker“ priority filing on 14 April 1949, published on 15 May 1952.

- ^ a b Lojek 2007, pp. 2–3.

- ^ 引用エラー: 無効な

<ref>タグです。「kilby」という名前の注釈に対するテキストが指定されていません - ^ a b Lojek 2007, p. 3.

- ^ “Who Invented the IC?”. Computer History Museum (20 August 2014). 20 August 2019閲覧。

- ^ Brock 2010, p. 36.

- ^ Hubner 1998, p. 100.

- ^ Hubner 1998, pp. 99–109.

- ^ Hubner 1998, p. 107.

- ^ a b c Brock 2010, pp. 36–37.

- ^ Lojek 2007, pp. 52, 54.

- ^ Lojek 2007, p. 82.

- ^ a b Lécuyer, Christophe; Brock, David C. (2010). Makers of the Microchip: A Documentary History of Fairchild Semiconductor. MIT Press. p. 111. ISBN 9780262294324

- ^ Saxena 2009, p. 97.

- ^ a b “Martin Atalla in Inventors Hall of Fame, 2009”. 21 June 2013閲覧。

- ^ a b Black, Lachlan E. (2016). New Perspectives on Surface Passivation: Understanding the Si-Al2O3 Interface. Springer. p. 17. ISBN 9783319325217

- ^ a b c d Lojek 2007, p. 120

- ^ Lojek 2007, pp. 321–323.

- ^ a b Bassett, Ross Knox (2007). To the Digital Age: Research Labs, Start-up Companies, and the Rise of MOS Technology. Johns Hopkins University Press. p. 46. ISBN 9780801886393 引用エラー: 無効な

<ref>タグ; name "Bassett46"が異なる内容で複数回定義されています - ^ Saxena 2009, p. 96.

- ^ “Dawon Kahng”. National Inventors Hall of Fame. 27 June 2019閲覧。

- ^ Saxena 2009, pp. 96–7.

- ^ Donovan, R. P. (November 1966). “The Oxide-Silicon Interface”. Fifth Annual Symposium on the Physics of Failure in Electronics: 199–231. doi:10.1109/IRPS.1966.362364.

- ^ Sah 1988, p. 1291.

- ^ a b Saxena 2009, pp. 100–101.

- ^ Saxena 2009, p. 100.

- ^ Sah 1988, p. 1290.

- ^ Brock 2010, pp. 30–31.

- ^ Lojek 2007, p. 126.

- ^ Lojek 2007, pp. 200–201.

- ^ a b c d e f Kilby 1976, p. 650.

- ^ a b Lojek 2007, p. 188.

- ^ Ceruzzi 2003, pp. 182–183.

- ^ a b c Lojek 2007, p. 191.

- ^ Ceruzzi 2003, p. 183.

- ^ Kilby 1976, pp. 650–651.

- ^ Saxena 2009, pp. 78–79.

- ^ Kilby 1976, p. 651.

- ^ Saxena 2009, pp. 82–83.

- ^ Kilby 1976, p. 652.

- ^ Saxena 2009, pp. 59–67.

- ^ Lojek 2007, p. 237-238.

- ^ “ARTICLES: Molecular Electronics - An Introduction”. Computers and Automation XI (3): 10–12, 14. (Mar 1962) 2020年9月5日閲覧。.

- ^ a b c Lojek 2007, p. 235.

- ^ a b Lojek 2007, p. 230.

- ^ a b Lojek 2007, pp. 192–193.

- ^ Lojek 2007, p. 231.

- ^ Lojek 2007, p. 236.

- ^ a b Lojek 2007, p. 237.

- ^ Lojek 2007, p. 238.

- ^ Lojek 2007, p. 201.

- ^ Berlin 2005, pp. 103–104.

- ^ Brock 2010, pp. 141–147.

- ^ a b c Brock 2010, pp. 144–145.

- ^ Brock 2010, pp. 157, 166–167.

- ^ Brock 2010, p. 157.

- ^ Brock 2010, p. 158.

- ^ Berlin 2005, p. 104.

- ^ Berlin 2005, p. 104-105.

- ^ Brock 2010, p. 39, 160–161.

- ^ Brock 2010, pp. 39, 161.

- ^ a b Saxena 2009, pp. 135–136.

- ^ Berlin 2005, p. 105.

- ^ Saxena 2009, pp. 237.

- ^ Saxena 2009, pp. 139, 165.

- ^ Berlin 2005, p. 111.

- ^ Berlin 2005, p. 111-112.

- ^ Lojek 2007, pp. 133, 138.

- ^ Lojek 2007, pp. 180–181.

- ^ a b Ceruzzi 2003, p. 188.

- ^ Ceruzzi 2003, p. 189.

- ^ Lojek 2011, p. 210.

- ^ a b “Computer Pioneers - James L. Buie”. IEEE Computer Society. 25 May 2020閲覧。

- ^ Lojek 2007, p. 211.

- ^ Lojek 2007, pp. 260–263.

- ^ “1960: Metal Oxide Semiconductor (MOS) Transistor Demonstrated”. Computer History Museum. 2024年5月2日閲覧。

- ^ “Who Invented the Transistor?”. Computer History Museum (4 December 2013). 20 July 2019閲覧。

- ^ Kuo, Yue (1 January 2013). “Thin Film Transistor Technology—Past, Present, and Future”. The Electrochemical Society Interface 22 (1): 55–61. Bibcode: 2013ECSIn..22a..55K. doi:10.1149/2.F06131if. ISSN 1064-8208.

- ^ “Tortoise of Transistors Wins the Race - CHM Revolution”. Computer History Museum. 22 July 2019閲覧。

- ^ “1964 – First Commercial MOS IC Introduced”. Computer History Museum. 2024年5月2日閲覧。

- ^ “Tortoise of Transistors Wins the Race - CHM Revolution”. Computer History Museum. 22 July 2019閲覧。

- ^ Kuo, Yue (1 January 2013). “Thin Film Transistor Technology—Past, Present, and Future”. The Electrochemical Society Interface 22 (1): 55–61. Bibcode: 2013ECSIn..22a..55K. doi:10.1149/2.F06131if. ISSN 1064-8208.

- ^ a b Lojek 2007, p. 195.

- ^ Lojek 2007, p. 239.

- ^ a b Lojek 2007, p. 176.

- ^ Sah 1988, p. 1292.

- ^ Lojek 2007, p. 240.

- ^ Lojek 2007, p. 241.

- ^ Lojek 2007, pp. 202–204.

- ^ Berlin 2005, p. 139.

- ^ a b c d Berlin 2005, p. 140.

- ^ a b Lojek 2008, p. 206.

- ^ Flamm 1996, p. 56.

- ^ Flamm 1996, pp. 56–57.

- ^ Flamm 1996, p. 57.

- ^ Flamm 1996, p. 58.

- ^ Flamm 1996, p. 68.

- ^ Flamm 1996, pp. 69–70.

- ^ Flamm 1996, p. 70.

- ^ Lojek 2007, p. 1.

- ^ Berlin 2005, p. 109.

- ^ Berlin 2005, pp. 140–141.

- ^ Berlin 2005, p. 141.

- ^ Lojek 2007, p. 194.

- ^ Lojek 2007, p. 2.

- ^ Rogers, Everett M.; Rafaeli, Sheizaf (1985). “Computers and Communication”. In Ruben, Brent D.. Information and Behavior. New Brunswick, NJ: Transaction Publishers. pp. 95–112. ISBN 978-0-887-38007-5. ISSN 0740-5502

- ^ Reid, T. R. (1984). The Chip: How Two Americans Invented the Microchip and Launched a Revolution. Simon and Schuster. p. 76. ISBN 978-0-671-45393-0. "One day in 1958, Jean Hoerni came to Noyce with a theoretical solution…"

- ^ Ceruzzi 2003, p. 179.

- ^ Ceruzzi 2003, p. 186.

- ^ Berlin 2005, p. 110.

- ^ Saxena 2009, pp. 335–340, 488.

- ^ Kaplan 2010, p. 76: "It was invented not by a vast team of physicists but by one man working alone, a self-described tinkerer – not even a physicist, but an engineer, John St. Clair Kilby".

- ^ Kaplan 2010, p. 266: "the microchip had a coincidental coinventor, Robert Noyce ... who came up with his own version of the idea in January 1959 but laid it aside. Only when he learned of TI's presentation in March 1959 trade show did he take another look...".

- ^ Saxena 2009, p. 59.

- ^ Berlin 2005, p. 109: "The wires precluded the device from being manufactured in any quantity, a fact of which Kilby was well aware, but his was undoubtably an integrated circuit … of sorts".

- ^ Lojek 2007, p. 15: "Historians assigned the invention of the integrated circuit to Jack Kilby and Robert N. Noyce. In this book I am arguing that the group of inventors was much bigger".

- ^ Lojek 2007, p. 194: "Kilby's idea of the integrated circuit was so unpractical that it was dropped even by Texas Instruments. Kilby's patent was used only as very convenient and profitable trading material. Most likely, if Jack Kilby worked for any company other than Texas Instruments, his idea would never have been patented.".

- ^ Saxena 2009, p. ix: "..prevailing view has been misleading, and has lasted for a long time, e.g., for more than four decades in this case of the invention of ICs … Almost everybody in the microelectronics field involving physics, chemistry, engineering etc in the entire world appear to have accepted the erroneous information of the IC invention for more than four decades because they have done nothing so far to correct it.".

引用エラー: <references> で定義されている name "NO" の <ref> タグは、先行するテキスト内で使用されていません。

引用エラー: <references> で定義されている name "braun" の <ref> タグは、先行するテキスト内で使用されていません。

引用エラー: <references> で定義されている name "r1" の <ref> タグは、先行するテキスト内で使用されていません。

引用エラー: <references> で定義されている name "r2" の <ref> タグは、先行するテキスト内で使用されていません。

引用エラー: <references> で定義されている name "r3" の <ref> タグは、先行するテキスト内で使用されていません。

引用エラー: <references> で定義されている name "r4" の <ref> タグは、先行するテキスト内で使用されていません。

引用エラー: <references> で定義されている name "r5" の <ref> タグは、先行するテキスト内で使用されていません。

引用エラー: <references> で定義されている name "r6" の <ref> タグは、先行するテキスト内で使用されていません。

引用エラー: <references> で定義されている name "CM621" の <ref> タグは、先行するテキスト内で使用されていません。

引用エラー: <references> で定義されている name "r8" の <ref> タグは、先行するテキスト内で使用されていません。

引用エラー: <references> で定義されている name "r9" の <ref> タグは、先行するテキスト内で使用されていません。

引用エラー: <references> で定義されている name "r10" の <ref> タグは、先行するテキスト内で使用されていません。

引用エラー: <references> で定義されている name "r11" の <ref> タグは、先行するテキスト内で使用されていません。

引用エラー: <references> で定義されている name "r12" の <ref> タグは、先行するテキスト内で使用されていません。

引用エラー: <references> で定義されている name "r13" の <ref> タグは、先行するテキスト内で使用されていません。

引用エラー: <references> で定義されている name "PJ" の <ref> タグは、先行するテキスト内で使用されていません。

引用エラー: <references> で定義されている name "Swain" の <ref> タグは、先行するテキスト内で使用されていません。

引用エラー: <references> で定義されている name "P299" の <ref> タグは、先行するテキスト内で使用されていません。

引用エラー: <references> で定義されている name "Seitz" の <ref> タグは、先行するテキスト内で使用されていません。

引用エラー: <references> で定義されている name "CM601" の <ref> タグは、先行するテキスト内で使用されていません。

引用エラー: <references> で定義されている name "L6" の <ref> タグは、先行するテキスト内で使用されていません。

引用エラー: <references> で定義されている name "bonch" の <ref> タグは、先行するテキスト内で使用されていません。

引用エラー: <references> で定義されている name "CM58" の <ref> タグは、先行するテキスト内で使用されていません。

引用エラー: <references> で定義されている name "Bassett" の <ref> タグは、先行するテキスト内で使用されていません。

引用エラー: <references> で定義されている name "j1" の <ref> タグは、先行するテキスト内で使用されていません。

引用エラー: <references> で定義されている name "Morris" の <ref> タグは、先行するテキスト内で使用されていません。

引用エラー: <references> で定義されている name "Huff" の <ref> タグは、先行するテキスト内で使用されていません。

<references> で定義されている name "P3029366" の <ref> タグは、先行するテキスト内で使用されていません。Bibliography

[編集]- Berlin, L. (2005). The Man Behind the Microchip: Robert Noyce and the Invention of Silicon Valley. New York: Oxford University Press. ISBN 9780199839773

- Brock, D.; Lécuyer, C. (2010). Lécuyer, C.. ed. Makers of the Microchip: A Documentary History of Fairchild Semiconductor. MIT Press. ISBN 9780262014243etal

- Ceruzzi, P. E. (2003). A History of Modern Computing. MIT Press. ISBN 9780262532037

- Flamm, K (1996). Mismanaged Trade: Strategic Policy and the Semiconductor Industry. Brookings Institution Press. ISBN 9780815728467

- Hubner, Kurt (1998). “The four-layer diode in the cradle of Silicon Valley”. In Tsuya; Huff; GöSele. Silicon Materials Science and Technology: Proceedings of the Eighth International Symposium on Silicon Materials Science and Technology. The Electrochemical Society. pp. 99–115. ISBN 978-1-56677-193-1

- Kaplan, F (2010). 1959: The Year Everything Changed. John Wiley & Sons. ISBN 9780470602034

- Lojek, Bo (2007). History of Semiconductor Engineering. Springer. ISBN 9783540342571 Internet Archive eBook ISBN 9783540342588.

- Sah, Chih-Tang (October 1988). “Evolution of the MOS transistor-from conception to VLSI”. Proceedings of the IEEE 76 (10): 1280–1326. Bibcode: 1988IEEEP..76.1280S. doi:10.1109/5.16328. ISSN 0018-9219.

- Saxena, A (2009). Invention of integrated circuits: untold important facts. International series on advances in solid state electronics and technology. World Scientific. ISBN 9789812814456

- tluong (2014年8月20日). “Who Invented the IC?” (英語). CHM. 2024年5月1日閲覧。

- “A mid-1960 implementation of the first Micrologic flip-flop using a... | Download Scientific Diagram”. ResearchGate. 2024年5月2日閲覧。

[[Category:集積回路]]

[[Category:計算機の歴史]]

[[Category:ドイツの発明]]

[[Category:アメリカ合衆国の発明]]

[[Category:未査読の翻訳があるページ]]