マンチェスター・コンピュータ

マンチェスター・コンピュータは1947年から1977年までの30年間にトム・キルバーン主導のもとマンチェスター・ビクトリア大学の少数精鋭チームが開発した一連の革新的なストアドプログラム方式の電子コンピュータ[1]のシリーズ。世界初のプログラム内蔵方式コンピュータ、世界初のトランジスタ式コンピュータ、1962年時点での世界最速のコンピュータなどがある[2][3][4][5]。

当初このプロジェクトには2つの目的があった。その1つは普通のブラウン管CRTをベースにした初期の記憶装置であるウィリアムス管に実用性があることを証明することだった。またもう1つはコンピュータが数学的な問題の解決に応用できるどうかを、実際にマシンを作って試してみることだった[1]。第1号機のマンチェスター・ベイビーは1948年6月21日に初めてプログラムが起動した[2]。世界初のプログラム内蔵方式コンピュータだったベイビーと、これをもとに作られたManchester Mark Iは、すぐに英国政府の関心を引き、政府は電子機器メーカーのフェランティに製品化を委託した。その結果作られたFerranti Mark 1は世界初の市販された汎用コンピュータとなった[1]。

フェランティとのコラボレーションはコンピュータ会社ICLとの産学連携事業に繋がり、大学が考案した様々なアイデアは、とりわけ1970年代のICL 2900シリーズのコンピュータ設計に活かされた[6][7][8]。

マンチェスター・ベイビー

[編集]マンチェスター・ベイビーは初期のコンピュータ用メモリであるウィリアムス管のテストベッドとして開発されたもので、実用化を目指したものではなかった。1947年から開発を始め、218 (262,144)の最大の約数を求めるために218-1から順に下へ向かって1つずつ整数の割り算を試す17個の命令で構成された最初のプログラムが1948年6月21日に動作した。プログラムは52分後に正解である131,072を出力した[9]。

ベイビーは長さ5.2m、高さ2.24m、重さ1.6トン(1英トン)あった。550本の真空管、300個のダイオード、250個の五極管が用いられ、消費電力は3.5kWだった[10]。この実験の成功は科学雑誌ネイチャーの1948年9月号で発表され[11]、世界初のプログラム内蔵方式コンピュータとして認知された[12]。これはすぐにManchester Mark Iとして実用化された。

Manchester Mark I

[編集]1948年8月にManchester Mark Iの開発が始まり、大学に実用的なコンピュータを提供することが当初の目的とされた[1]。1948年10月に英国政府の主任科学者であるベン・ロックスパイザーがプロトタイプのデモンストレーションを見学して感動し、すぐに政府が地元企業のフェランティと随意契約を結んで商用版のFerranti Mark 1を製造するよう手配した[1]。

Manchester Mark Iは2台製造されており、うち1台の暫定版は1949年4月に稼働した[1]。完全版は1949年10月に完成し[13]、4050個の真空管が使われ消費電力は25kWだった[14]。Manchester Mark Iで最も革新的だったのはインデックスレジスタで、現代のコンピュータでは存在するのが当たり前になっている[1]。

MegとMercury

[編集]開発者たちはMark Iの経験からコンピュータは純粋な数学の問題を解決することよりも科学分野で役立つということを学んだ。これを受け1951年から浮動小数点演算器を搭載した次世代機の開発に着手した。1954年5月にメガサイクルマシンのMegで最初のプログラムが動作した。Mark Iよりも小型かつシンプルで、数学の問題をより高速に処理できた。フェランティはこれの商用バージョンをFerranti Mercuryとして開発し、ウイリアムス管はより信頼性の高いコアメモリに置き換えた[1]。

トランジスタ・コンピュータ

[編集]Megの開発と並行して、より小型で安価なコンピュータの開発が1952年に始まった。真空管ではなく、新たに開発されたトランジスタを使ったマシンを設計する作業に、キルバーンのチームからリチャード・グリムズデールとD.C.ウェブの2人が割り当てられた。当初はゲルマニウム点接触型トランジスタしか使用できず、真空管より信頼性で劣っていたが、消費電力は大幅に削減された[1]。

2台のマシンが製造された。1台目は世界初のトランジスタ・コンピュータ[1]のプロトタイプで、1953年11月16日に稼働した[3][15]。この48ビット機には92個の点接触型トランジスタと550個のダイオードが使われた。1955年4月に完成した2台目は250個の点接触型トランジスタ[16]と1,300個の半導体ダイオードが使われ、消費電力は150Wだった。しかし125kHzのクロックを生成するためと、磁気ドラムメモリを読み書きする回路で真空管が使われており、完全にトランジスタ化されたコンピュータという名声は1955年のHarwell CADETに奪われた[17]。

初期のトランジスタには信頼性に問題があったことから平均故障間隔は約90分で、この問題はより信頼性の高いバイポーラトランジスタの登場とともに改善した[1]。地元のゼネコン企業であるメトロポリタン・ヴィッカーズはこのトランジスタ・コンピュータをベースに、全ての回路をバイポーラトランジスタに変更したMetrovick 950を開発した。Metrovick 950の1台目は1956年に完成し、最終的に6台が製造された。これらは社内の様々な部署に配備されて5年間に渡り使われた[1]。

MuseとAtlas

[編集]マンチェスター大学は1956年に「マイクロセカンドエンジン」を意味するMUSEの開発を始めた。1µsに1命令、1秒間に100万命令を実行できるコンピュータを製作することが目標だった[18]。マイクロ(Muまたはµ)は国際単位系(SI)の接頭語で、10-6 (百万分の1)を表す。

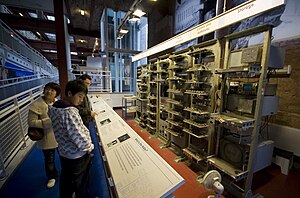

フェランティは1958年の終わりにマンチェスター大学のプロジェクトに協力することで同意し、その直後にコンピュータの名前をAtlasに変更し、この産学連携事業をトム・キルバーンが監督することになった。Atlasの第1号機は1962年12月7日に正式に納入され、IBM 7094の4倍の性能があり、当時は世界一の性能を持つコンピュータと言われた[1]。Atlasが停止するとイギリスのコンピュータ総演算能力が半分になると言われた[1]。最も高速な命令は1.59µsで処理され、仮想メモリとページング(スワップ)により各ユーザーが最大100万ワードのメモリを同時に利用できるようになった。Atlasのハードウェアとソフトウェアが導入した様々な新しいコンセプトは今日では広く使われており、中でもOSのAtlas Supervisorは現代の概念で言う所のOSとして最初のOSだとされている[19]。

Altasは他にも2台が製造された。1台はブリティッシュペトロリアムとロンドン大学が共同で使用し、もう1台はオックスフォード近くのチルトンにあるアトラスコンピュータ研究所に設置された。またフェランティはメモリ構成が異なる改良版のTitan(Atlas 2)をケンブリッジ大学に納入しており、ケンブリッジ大学コンピュータ研究所が開発したタイムシェアリングOSが動作した[1]。

マンチェスター大学のAtlasは1971年に運用を終えたが[1]、1974年まで動いていた[1]。チルトンで動いていたAtlasのパーツはエディンバラのスコットランド国立博物館に残されている。

MU5

[編集]MU5に関する詳細な記事はEngineering and Technology History Wikiを参照。

1968年にエジンバラで開催されたIFIP会議でAtlas後継機の草案が発表[20]されたが、フェランティを吸収したICTに支援を求める話し合いは1966年から既に始まっていた。新機種は後にMU5と呼ばれ、世界一の性能を達成すべくAtlasの20倍の性能を目指した。

1968年に科学技術研究評議会SRCは新機種の開発費としてマンチェスター大学へ5年で£630,466(2016年の価値で£9300万に相当) の助成金を支給し、後にICLとなったICTがその製造ラインを大学に提供した。その年にはコンピュータサイエンス部門のスタッフ11人、ICTからの出向スタッフ5人、SRCのサポートスタッフ4人からなる20人が設計チーム人参加した。スタッフの人数が最も多かったのは1971年で、大学院生を含めて60人に上った[21]。

MU5プロセッサで最も革新的だったのはそのインストラクションセットであり、連想メモリを活用することでオペランドとインストラクションのアクセスを高速化していた。インストラクションセットはコンパイラが効率のよいオブジェクトコードを出力できるよう設計されており、プロセッサのパイプライン化を可能にし、オペランドの意味に関する情報をハードウェアに提供し、データを適切にキャッシュできるようになっていた。名前付き変数は配列要素とは別の場所にバッファリングされ、ディスクリプタにより名前でアクセスすることができた。ディスクリプタにはサイズの情報が含まれており、文字列処理や配列処理でハードウェアによる境界チェックが可能だった。インストラクションをプリフェッチするメカニズムは分岐予測に用いられた[22]。

MU5のOSであるMUSS[23][24]は非常に移植性が高い設計となっており、マンチェースター内外の様々なプロセッサに移植された。完成したMU5システムは、高速ネットワークシステムのExchangeにより、MU5自身、ICL 1905E、PDP-11といった3つのプロセッサに加え、様々なメモリデバイスや周辺機器と接続することができた[25][24]。これら3つのプロセッサには全てそれぞれ用のMUSSがあった。MUSSはまた様々なプログラミング言語のコンパイラに対応しており、コンパイルされたプログラムを動作させるためのランタイムパッケージが含まれていた。カーネルの構造は小型化されており、各機種毎にバーチャルマシン[注釈 1]のサブシステムが移植された。MUSSのコードは各バーチャルマシンの仮想メモリ上の共通部分から参照できた。

MU5は1974年10月までに完成して動作し、ほぼ同時にICLは新世代機である2900シリーズの開発に取り組んでいることを発表した。特に1975年6月に出荷されたICLの2980はMU5の設計ほぼそのままだった[26]。MU5は1982年まで大学で運用された[27]。

MU6

[編集]MU5の稼働が本格化すると、後継機のMU6を開発するプロジェクトがスタートした。高性能マイコンを搭載したパソコンのMU6P[28]、科学技術計算アプリケーションなどに対応した高性能マシンのMU6-G[29]、並列ベクトル処理システムのMU6V[30]など、MU6は複数のカテゴリに渡るラインナップを想定して設計された。68000マイクロプロセッサをベースに、エクストラコード[注釈 2]でベクトル演算器をエミュレートしたものをMU6Vのプロトタイプとして実験的に製作したが、MU6Vの開発はここで打ち切られた。MU6-GはSRCからの助成金を受けて制作され、1982年から1987年までうまく稼働し[4]、OSにはMU5プロジェクトで開発されたMUSSが用いられた。

年表

[編集]| 年 | 大学のプロトタイプ | 年 | 商用版 |

|---|---|---|---|

| 1948 | マンチェスター・ベイビー、後のManchester Mark I | 1951 | Ferranti Mark 1 |

| 1953 | トランジスタコンピューター | 1956 | Metrovic 950 |

| 1954 | Manchester Mark IIまたはMeg | 1957 | Ferranti Mercury |

| 1959 | Muse | 1962 | Ferranti Atlas、Titan |

| 1974 | MU5 | 1974 | ICL 2900シリーズ |

出典

[編集]- ^ a b c d e f g h i j k l m n o p q Lavington (1998).

- ^ a b Enticknap, Nicholas (Summer 1998), “Computing's Golden Jubilee”, Resurrection (The Computer Conservation Society) (20), ISSN 0958-7403, オリジナルの9 January 2012時点におけるアーカイブ。 19 April 2008閲覧。

- ^ a b Grimsdale. “50th Birthday of Transistor Computer”. curation.cs.manchester.ac.uk. 24 February 2018閲覧。

- ^ a b “A Timeline of Manchester Computing”. University of Manchester. 5 July 2008時点のオリジナルよりアーカイブ。25 February 2009閲覧。

- ^ The Virtual Museum of Manchester Computing: Timeline of Manchester Computing

- ^ Lavington, Simon (1980), Early British Computers, Manchester University Press, ISBN 978-0-7190-0803-0

- ^ Lavington, Simon (1998), A History of Manchester Computers (2nd ed.), The British Computer Society, ISBN 978-1-902505-01-5

- ^ Napper, R. B. E. (2000), “The Manchester Mark 1 Computers”, in Rojas, Raúl; Hashagen, Ulf, The First Computers: History and Architectures, MIT Press, pp. 356–377, ISBN 978-0-262-68137-7

- ^ Tootill, Geoff (Summer 1998), “The Original Original Program”, Resurrection (The Computer Conservation Society) (20), ISSN 0958-7403, オリジナルの9 January 2012時点におけるアーカイブ。 19 April 2008閲覧。

- ^ Manchester Museum of Science & Industry (2011年). “The "Baby": The World's First Stored-Program Computer”. MOSI. 15 February 2012時点のオリジナルよりアーカイブ。3 April 2012閲覧。

- ^ Williams, F. C.; Kilburn, T. (25 September 1948), “Electronic Digital Computers”, Nature 162 (4117): 487, Bibcode: 1948Natur.162..487W, doi:10.1038/162487a0, オリジナルの6 April 2009時点におけるアーカイブ。 22 January 2009閲覧。

- ^ Napper (2000).

- ^ Napper. “The Manchester Mark 1”. University of Manchester. 9 February 2014時点のオリジナルよりアーカイブ。22 January 2009閲覧。

- ^ Lavington (July 1977). “The Manchester Mark 1 and Atlas: a Historical Perspective”. University of Central Florida. 8 February 2009閲覧。. (Reprint of the paper published in Communications of the ACM (January 1978) 21 (1)

- ^ Neumann, Albrecht J. (Apr 1955) (英語). COMPUTERS, Overseas: 5. Manchester University - A SMALL EXPERIMENTAL TRANSISTOR DIGITAL COMPUTER. 7. pp. 16–17.

- ^ “1953: Transistorized Computers Emerge | The Silicon Engine | Computer History Museum”. www.computerhistory.org. 2019年9月2日閲覧。

- ^ Cooke-Yarborough, E. H. (June 1998), “Some early transistor applications in the UK”, Engineering Science & Education Journal (IEE) 7 (3): 100–106, doi:10.1049/esej:19980301, ISSN 0963-7346 7 June 2009閲覧。 (

要購読契約)

要購読契約)

- ^ “The Atlas”. University of Manchester. 28 July 2012時点のオリジナルよりアーカイブ。21 September 2010閲覧。

- ^ Lavington (1980).

- ^ Kilburn, T.; Morris, D.; Rohl, J.S.; Sumner, F.H. (1969), “A System Design Proposal”, Information Processing 68, 2, North Holland, pp. 806–811

- ^ Morris, Derrick; Ibbett, Roland N. (1979), The MU5 Computer System, Macmillan

- ^ Sumner, F.H. (1974), “MU5 - An Assessment of the Design”, Information Processing 74, North Holland, pp. 133–136

- ^ Frank, G.R.; Theaker, C.J. (1979), “The design of the MUSS operating system”, Software Practice and Experience 9 (8): 599–620, doi:10.1002/spe.4380090802

- ^ a b Morris & Ibbett (1979).

- ^ Lavington, S.H.; Thomas, G.; Edwards, D.B.G. (1977), “The MU5 Multicomputer Communication System”, IEEE Trans. Computers, C-26, pp. 19–28

- ^ Buckle, John K. (1978), The ICL 2900 Series, The Macmillan Press

- ^ Ibbett, Roland N. (1999), “The University of Manchester MU5 Computer Project”, Annals of the History of Computing (IEEE) 21: 24–31, doi:10.1109/85.759366

- ^ Woods, J.V.; Wheen, A.J.T. (1983). “MU6P: an advanced microprocessor architecture”. The Computer Journal 26 (3): 208–217. doi:10.1093/comjnl/26.3.208.

- ^ Edwards, D.B.G; Knowles, A.E.; Woods, J.V. (1980), “MU6-G: a new design to achieve mainframe performance from a mini-sized computer”, 7th Annual International Symposium on Computer Architecture, pp. 161–167, doi:10.1145/800053.801921

- ^ Ibbett, R.N.; Capon, P.C.; Topham, N.P. (1985), “MU6V: a parallel vector processing system”, 12th Annual International Symposium on Computer Architecture, IEEE, pp. 136–144