論理回路

論理回路(ろんりかいろ、英: logic circuit)とは、デジタルな電子回路による、論理演算や記憶を行う回路である[注 1]。

概要

[編集]真理値の「真」と「偽」、あるいは二進法の「0」と「1」を、電圧の正負や高低、電流の方向や多少、位相の差異、パルスなどの時間の長短、などで表現し、論理素子など[注 2]で論理演算を実装する。電圧の高低で表現する場合それぞれを「

表記法

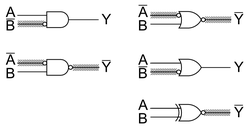

[編集]論理回路の設計には、論理式や真理値表が用いられる。さらに回路図的な表記手段としてMIL記号など論理素子記号が使われる。

負論理には正論理の信号名の上にオーバーバー(例: )を加えることで表現し、MIL記号では小丸(○)で表現する[1]。

正論理・負論理

[編集]MIL記号を含めて通常のロジック・ダイアグラム[注 4]では正論理と負論理が混在して使用される。

正論理では「H」を真偽値の「真」に、負論理では「L」を真偽値の「真」に対応させる。

厳密には正論理の出力信号線は必ず正論理の入力に接続されねばならず、負論理出力は負論理の入力に接続されねばならないが、図面上の表記として必ず守られるとは限らない[1](「厳密には」というよりは、図面の目的による。たとえば、論理的な動作を理解するための図であるのか、製造のための電子的な回路図に近い性格のものであるのか、結局のところケースバイケースであろう)。

組み合わせ回路

[編集]組み合わせ回路[注 5]は、現在の入力のみで出力が決まる回路である。

- 論理ゲート:

ANDゲート(AND,アンド)、ORゲート(OR,オア)、NOTゲート(NOT,ノット)、XORゲート(XOR,エクスクルーシブ・オア)

など基本となる論理演算を行うものである。

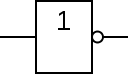

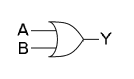

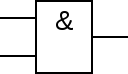

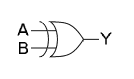

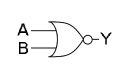

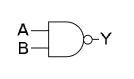

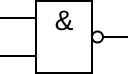

| 論理 | 論理式 | 回路記号(MIL記号) | 回路記号(JIS記号) |

|---|---|---|---|

| NOT |

| ||

| OR |

|

| |

| AND |

|

| |

| XOR |

|

| |

| NOR |

|

| |

| NAND |

|

|

- エンコーダ:複数の入力の内の1つが「真」になった時にそれに対応する2進数コードを出力するもの。

- デコーダ:2進数のコード入力に対応して、多数の出力線の内の1本だけを「真」にするもの。

- マルチプレクサ:2進コード入力に基づいて、複数の入力から1つを選んで出力するもの。「データセレクタ」[注 6]とも呼ばれる。

- デマルチプレクサ[注 7]:2進コード入力に基づいて、1つの入力を複数の出力の内の1つに出力するもの。

- 加算器 : 2進数の加算を行うもの。全加算器[注 8]と半加算器[注 9]があり、多桁の全加算器では桁上げの高速化の為に「キャリールックアヘッド回路」を備えるものもある。負の数の表現に2の補数を使っているのであれば、減算は2の補数を加算することで実現出来る。回路規模が大きくなってもわずかでも高速化したい場合、減算に対応するための論理反転の追加(XORを1段または、NOTを1段とセレクタを1段)を避け、専用の減算回路を持つこともある。半減算器はXORであって半加算器と全く同じであるから、減算器には全減算器[注 10]しか無い。

- 乗算器:2進数の乗算を行うもの。過去にはALU上で加算とシフトの繰り返しで乗算を行っていたが、近年は多数のゲート回路によって一度に乗算してしまう専用乗算器が使用されている。

- バレルシフタ:シフトレジスタによるシフト操作では移動のビット数分の回数だけクロックの動作時間が掛かるが、これを避けるためにマルチプレクサを複数組並べるのと同様に多数のゲート回路によって一度にずらすことで実現するものである。

- 比較器[注 11]:「ディジタル・コンパレータ」とも呼ばれ、概念としては一致回路や不一致回路、大小を比較する比較器もあり[1]、実際のロジックICでは4ビットや8ビットの比較器にこれら全ての信号が出力されるものが多い[2]。

- transmission gate: (en:Transmission gate)働きとしては入出力の間の電気的な直結あるいは絶縁の状態を切り替えるスイッチなので、ディジタルに限らずアナログにも使えるゲートだが、XORゲートの実装など論理回路にも有用な応用がある。

順序回路

[編集]順序回路は過去の内部状態と取得時の入力信号とで出力が決まる回路である。組み合わせ回路は、伝播遅延によって信号が遅れることを除けば、入力の組み合わせだけで出力が一意に決まるが、順序回路はループにより内部に状態を保持しており、過去の入力に影響されるその状態も、出力の決定に関わる。入力信号の組み合わせによっては「不定」になる場合がある[3](ラッチ回路#SRラッチの「不定」)。

フリップフロップ

[編集]フリップフロップは制御信号により現在の入力信号の保持を行うものである。ラッチとも呼ばれる。論理回路ではフリップフロップと呼ぶものも、コンピュータ・システムでの回路名としては(通常は複数ビットの記憶回路を)レジスタと呼ぶ。

非同期式フリップフロップはクロック入力を持たず、その時点での入力の値に応じて出力が変化し、新たな入力信号が来るまで同じ状態を保持する。

- 非同期式RS-FF(=RSラッチ):標準ではRとSが共に「真」は禁止されているが、セット優先、リセット優先のものでは両入力が共に「真」の時にはセットにだけ「真」の入力があったもの、またはリセットにだけ 「真」 の入力があったものとして扱われる設定が行なえるものがある。

- 非同期式D-FF(=Dラッチ):RS-FFのS入力にストローブ入力(G)によるゲート制御が加わったものである。ストローブが 「真」 の間はD入力はQ出力にそのまま反映され、ストローブが「真」から「偽」に変わるとその変化時点(立ち上り、又は立ち下り)での入力を保持する。

同期式フリップフロップはクロック信号(CLK、CK等と表記)の立ち上がり(又は立ち下り)に同期してその時点での入力(D, S, J等)に対応する信号を出力する。この出力は次にクロックが立ち上がる(又は立ち下る)まで更新されない。

- 同期式RS-FF:RS は reset と set から付けられた。

- 同期式D-FF:D は data または delay から付けられた。

- JK-FF:RS-FFの動作に近いがRとSの両方が「真」の時は出力が反転するのでRとSに同じ入力を与えると同期式T-FFとして動作する。JとKに互いに反転した入力を与えればD-FFとなる。もちろんRS-FFとして使用できる。このため、JK-FFは色々な構成で使用される。内部には2段の非同期FFがマスター・スレーブ構成に並んでいて、同期動作を行なっている。

- T-FF:クロックやクリア、プリセット以外の入力は持たず、クロックが入力されるたびに出力が反転する。Tは toggle から付けられた。

カウンタ

[編集]カウンタ回路は、特定の順序で出力の組み合わせが変化し、一定の周期で元の状態に戻るもので、フリップフロップとゲートとをいくつか組み合わせたものである。

- シフトレジスタ:直列フリップフロップの入力と出力を直接接続したもので、クロックに合わせて各FFを1段ずつ横に送っていく(シフトしてゆく)動作をするもの。通常は初段と終段の間は接続されていない。

- ジョンソン・カウンタ:シフトレジスタの初段と終段の間だけ入力と出力を反転して接続したもの。クロックに合わせて各FFを1段ずつ横に送っていく(シフトしてゆく)動作をするが、反転入力が移動してゆくので n 段ならば 2n 回目で一順するカウンタとなり、初期値が単純に「0」や「1」ばかりであればデューティサイクルが50%のディジタル波形信号が得られる。

- リング・カウンタ:シフトレジスタの初段と終段の間も他の段同様、入力と出力を直接接続したもの。初期値で設定されたディジタル波形信号がn回目で一順するカウンタとなる。例えば4段リング・カウンタに

1000と設定すれば0100→0010→0001→1000となって4回目で元に戻る。 - バイナリ・カウンタ(2進カウンタ)

- n進カウンタ:(同期式であれば)バイナリ・カウンタのリセット入力に n-1 回目で「H」となるようにゲート回路で信号を接続する。n 回目のクロック入力でリセットがかかり、全てが

0に戻る。

また、全ての出力状態が使用されるものと出力状態の一部のみ使用されるものの差で次の2つのグループに分類出来る。

- フィルド・コード・カウンタ[注 12]:全ての出力状態が使用されるもの。

- 2ビットジョンソン・カウンタ

- グレイ・コード・カウンタ、

- バイナリ・カウンタ(2進カウンタ)

- アンフィルド・コード・カウンタ[注 13]:出力状態の一部のみ使用されるもので、その他の状態になる時は動作不良のときであるもの。

- 3ビット以上のジョンソン・カウンタ

- リング・カウンタ

- M系列発生器(線形帰還シフトレジスタ[注 14])

カウンタには同期式と非同期式があり、非同期式カウンタは常に前段の結果によって次段の動作が左右されるため、多段になるほど終段の結果の確定は回路の伝播遅延による遅れが蓄積される。こうしたものは「非同期式リプルカウンタ」と呼ばれる。

多くのカウンタ回路には、加算と減算の動作選択、各段の初期値のプリセット、全段のリセットなどの機能を備えており、また、論理回路的な設計とは無関係であるが実際のICチップパッケージには多段接続時に数珠繋ぎに延長できるよう、キャリアアウト出力とキャリアイン入力と云う桁上げ出力や桁借り出力などが備わっている[1]。

同期と非同期・他

[編集]以上の、組合わせ回路と順序回路という分類とは別に、以下のような分類もある。

同期

[編集]同期式では非同期式に比べて信号の遅れやレーシングといった問題に起因する動作不良が減らせる、又は根絶できるが、回路規模が大きくなるので消費電力や回路コストが増す[1]。非同期式は単純な回路構成が採れるので低消費で回路コストも安くて済み、回路設計が最適化出来れば高速動作が可能になるが、設計マージンが小さくなる傾向があり小さなミスが動作不良に結びつく。

特に完全同期式回路は、全体で共有するクロック信号を利用して動作のタイミングをあわせる回路である(クロック同期設計)。大規模な回路で広く用いられている。設計時に大規模な回路のシミュレーションが行いやすい、製造時に全てのラッチの 1・0 が切り替わるかどうかのテストを行う試験機のプログラムを作成しやすい、といった利点がある。

非同期

[編集]同期式に対し、別に同期信号を持たないものが非同期式で、非同期論理・非同期回路(en:Asynchronous circuit)と言う。電気試験所のETL Mark IとMark II、富士通のFACOM 128などのリレー式計算機に採用がある。マイクロプロセッサでは、商業的に販売されてはいないがAMULETや南谷研の「TITAC」がある。

動的と静的

[編集]DRAMのように、常に活動していなければ正常に動作しない論理回路を動的と言う。これに対し、SRAMのように、電圧の供給だけで働く論理回路を静的と言う。マイクロプロセッサのレジスタのように多くの記憶が必要な場合、素子数の点で有利な動的回路の場合があり、そういったマイクロプロセッサは動作周波数に下限があり、また、クロックを止めることができない。

論理演算に対しても、常に働く回路として論理演算をおこなうものを静的論理と言う。汎用ロジックICの多くなど、現在使われている多くの論理回路は静的である。これに対し、クロックに合わせ1クロックで1段階の論理演算を行うような方式もあり、動的論理(en:Dynamic logic (digital electronics))と言う。電気試験所のETL Mark III・IV、パラメトロンの回路方式、トランスピュータの内部回路などに実例がある。

その他

[編集]論理回路というよりディジタル回路としての分類になるが、以下のようなデバイスがある。

- ワイヤード・オア[注 15]:(TTLでは)複数のオープンコレクタ出力を使って便宜上のOR回路を構成する手法。通常は複数のディジタル出力をそのまま結線することは許されないが、オープンコレクタ出力により可能となる。プルアップ抵抗が必要。CMOSではオープンドレインとなる。

- バッファ[注 16]、バス・トランシーバ[注 17]、ライン・ドライバ/レシーバ[注 18]:伝送路や多数のゲートを駆動する為に大きな出力の回路を持つもの。多くが4bit、8bit、16bitなどの複数本を並列にして扱われる。

- トライステート・バッファ[注 19]:バッファの出力状態を「H」と「L」の他にハイ・インピーダンス[注 20]の合計3つ持つもの。

- シュミット・トリガ[注 21]:不安定な入力信号を安定的に波形整形して出力する為に、ヒステリシス特性を備えたアンプを持つ。インバータ回路などに多い[1]。

- シーケンサ[注 22]:外部状況の変化にしたがって定義された演算・動作を行うもので、カウンタ・外部信号のレジスタ・ゲートなどを組み合わせて製作される。

歴史

[編集]電気による論理演算は、リレー(ことによってはソレノイドアクチュエータやモータと、スイッチ)による装置(たとえば初期の電話交換機など)があった。しかし、ブール代数は19世紀中頃に考案されていたが、当時はそれらの装置と関連付けて考えられていなかった。

ディジタル回路と論理演算の対応付けは、中嶋章が1934年頃から研究、論文としては1936-1937年[注 23]に榛沢正男と発表した「継電器回路に於ける単部分路の等価変換の理論」を嚆矢とし、クロード・シャノンの1937年の研究とその発表が有名である(他にも相次いで発表されている)。後者の着想が独立かどうかは不明である[4]。

個別部品時代もモジュール化はおこなわれていたが、1960年代に登場した汎用ロジックICにより、アナログ的な回路設計と論理設計をほぼ分離できるようになった。

小規模な場合は、論理素子記号などを使った手書きによる設計が可能であるが、大規模になると難しい。そのため、大規模な回路の設計にはハードウェア記述言語(HDL)が多用されるようになった。

1990年代後半より、試作や少量生産の場合に論理がプログラマブルな(書き換え可能な)PLDやCPLD、FPGAなどが使用されるようになった。大量生産または高性能が要求される場合はASICも使用される。

その他

[編集]- 十進法で表現された数を、整数値として2進に変換するのではなく扱う方法として二進化十進表現がある。

0000から1001を使用し1010から1111は使用しないというよくある方法の他いくつかのバリエーションや、近年の十進浮動小数点で使われている10ビットに十進3桁を詰め込む densely packed decimal、3増し符号、2-5進コード(二五進法)などがある。

脚注

[編集]注釈

[編集]- ^ リレーによるものは「電子回路」というよりは「電気回路」だが、この記事ではほとんど扱わない。また真理値が連続的な値をとる(アナログな)論理を扱う論理回路や、アナログ電子回路による論理回路、流体素子や光コンピューティングといった電気以外による論理演算の提案などについても、以下の説明では全く考慮していない。

- ^ ワイヤードORなどは論理素子による実装ではない。

- ^ そのようにすると、たとえば図で、2入力1出力のANDの3個の端子全てに小丸が付いていた場合、負論理として見ると論理積の働きをしている(電気的にはORゲートである)ということがわかりやすくなり都合が良い。

- ^ 英: logic diagram

- ^ 「組み合わせ論理回路」ともいう。

- ^ 英: data selector

- ^ 英: demultiplexer

- ^ 英: full adder

- ^ 英: half adder

- ^ 英: full subtracter

- ^ 英: comparator

- ^ 英: filled code counter

- ^ 英: unfilled code counter

- ^ 英: linear feedback shift register

- ^ 英: wired OR

- ^ 英: buffer

- ^ 英: bus transceiver

- ^ 英: line driver/receiver

- ^ 英: 3-state buffer

- ^ 英: high impedance

- ^ 英: Schmitt trigger

- ^ 英: sequencer

- ^ 2部構成

出典

[編集]- ^ a b c d e f 松田勲著 『ディジタルIC回路の基礎』 技術評論社 2005年7月1日 初版第5刷発行 ISBN 4-7741-0804-9

- ^ 最新汎用ロジック・デバイス規格表 CQ出版社 2006年1月1日発行 ISBN 4-7898-4459-5

- ^ TI SN74HC74 データシート、TI SN74LS279A データシート

- ^ 山田昭彦、「スイッチング理論の原点を尋ねて -シャノンに先駆けた中嶋章の研究を中心に-」 『子情報通信学会 基礎・境界ソサイエティ Fundamentals Review』 2010年 3巻 4号 p.4_9-4_17, doi:10.1587/essfr.3.4_9

関連項目

[編集]- 集積回路

- 数理論理学

- シーケンス制御

- 論理診断

- ブール論理 - ブール関数 - ブール代数

- 選言標準形 - 連言標準形

- 負論理 - 正論理

- 標準ロジックIC

- ディジタル回路

- CPU設計

- プログラマブルロジックデバイス