Zen 2

| 生産時期 | 2019年7月から |

|---|---|

| 販売者 | AMD |

| 設計者 | AMD |

| 生産者 |

TSMC (CPUダイ) Global Foundries (I/Oダイ) |

| プロセスルール |

7 nm (CPUダイ)[1][2] 14 nm (I/Oダイ) (APUは全て7 nm) |

| 命令セット | AMD64 |

| コア数 |

4-16 (メインストリーム) 8-64 (HEDT・サーバー) |

| ソケット |

Socket AM4 (メインストリーム) Socket SP3 (サーバー) Socket sTRX4 (HEDT) |

| コードネーム |

|

| 前世代プロセッサ | Zen |

| 次世代プロセッサ | Zen 3 |

| L1キャッシュ | コア当たり64 KiB |

| L2キャッシュ | コア当たり512 KiB |

| ブランド名 | Ryzen、EPYC |

Zen 2(ゼン・ツー)とは、AMDによって開発されたCPUマイクロアーキテクチャのコードネームである。AMDのZen、Zen+マイクロアーキテクチャの後継にあたり、TSMC製7 nmMOSFET素子により製造されている。メインストリーム・デスクトップ用のRyzen 3000 (コードネーム Matisse)、ハイエンド・デスクトップ用のThreadripper 3000[3][4]、APU用のRyzen 4000Gとして知られる、第3世代Ryzenプロセッサに使われている。2019年7月7日にRyzen 3000シリーズCPUが発表され[5][6]、2019年8月7日にZen 2ベースのEPYCサーバーCPU (コードネーム Rome)が発表された[7]。2019年11月に追加のチップセット、Ryzen 9 3950Xが発表された[5]。CES 2019において、AMDは8コア16スレッドのチップレットを含む、第3世代Ryzenのエンジニアリングサンプルを発表した[3]。AMDのCEOリサ・スーは、最終的なラインナップでは8コアより多いチップを予定していると述べた[8]。Computex 2019において、AMDはZen 2 "Matisse"プロセッサが12コアとなることを明らかにし、数週間後のE3 2019では16コアプロセッサである先述のRyzen 9 3950Xを明らかにした[9][10]。

Zen 2にはSpectreに対するハードウェアによる脆弱性緩和が含まれている[11]。Zen 2ベースのEPYCサーバーCPUでは、各マルチチップ・モジュール(MCM)パッケージにおいて、7 nmプロセスで製造された複数のCPUダイ(合計8個まで)と、14 nm I/Oダイを組み合わせる設計を採っている。これにより、ソケット当たり最大64個の物理コアと合計128個の計算スレッド(同時マルチスレッディング)をサポートすることができる。このアーキテクチャは、「プロコンシューマ」向けフラッグシッププロセッサであるThreadripper 3990Xのレイアウトとほぼ同じである[12]。Zen(14 nmマイクロアーキテクチャ、第1世代Ryzen)、Zen+(12 nmマイクロアーキテクチャ、第2世代Ryzen)に比べ、Zen 2はクロックあたりの命令実行数(IPC)が約15%向上している[要出典]。

設計

[編集]Zen 2は、ZenやZen+に使われていたAMDの前世代Zenアーキテクチャの物理的設計パラダイムから大きく逸脱している。Zen 2は、CPUのI/Oコンポーネントが個別のダイにレイアウトされるような、チップレットとも呼ばれるマルチチップ・モジュール設計に移行している。その結果、スケーラビリティと製造コストが向上している。プロセス技術による物理的インターフェイスの縮小には限度があるため、I/Oコンポーネントを別のダイに分離することによってCPUダイより大きく、高性能にすることに成功している。このCPUダイ(AMDは「Core Complex Die」、CCDと呼んでいる)は、I/Oコンポーネントを別のダイに分離したためによりコンパクトになっているため、大きいダイと比べてより小さいプロセスルールで、欠陥品もより少なく製造できる。また、ダイが欠陥品となる確率はダイの大きさに比例するため、一つのウェハーからより多くのダイを切ることができる。加えて、中央のI/Oダイは複数のチップレットで共有できるため、多数のコアを持つプロセッサを設計することが容易になる[13][14][15]。

各CPUに8コアが搭載されているZen 2には、4コアの「コア・コンプレックス」(CCX)が2つずつ配置されている。これらのチップレットはTSMC製7 nmMOSFET素子が使われており、大きさは74 - 80 mm2程である[14]。 このチップレットに約39億個のトランジスタが使われているのに対して、12 nmのIOD (I/Oダイ)には約125 mm2の大きさに20.9億個のトランジスタしか使われていない[16]。 L3キャッシュの大きさは、ZenやZen+が8 MiBであったのに比べ、8コアチップレットの各コアが16 MiBにアクセスできるため、32 MiBに倍増している[17]。実行単位の幅が128ビットから256ビットになっているため、AVX2の性能が大幅に向上している[18]。

I/Oダイには複数のバリエーションがあり、GlobalFoundriesの14 nmプロセスのものや、同社の12 nmプロセスのものがある。14 nmダイは多機能であり、EPYC Romeプロセッサに使われている一方、12 nm版はコンシューマ向けプロセッサに使われている[14]。どちらのプロセスも寸法が似ているため、トランジスタ密度もほぼ同じである[19]。

AMDのZen 2アーキテクチャはインテルのCascade Lakeマイクロアーキテクチャより低い消費電力でより高いパフォーマンスを実現できる。一例として、Intel Core i9-10980XE (TDP 165W)よりもAMD Ryzen Threadripper 3970X (TDP 140W、エコモード)の方が高いパフォーマンスを実現している[20]。

新機能

[編集]- 新命令の追加: WBNOINVD、CLWB、RDPID、RDPRU、MCOMMIT。各命令は自身のCPUID ビットを用いる[21][22]。

- Spectre V4投機的ストアバイパス脆弱性に対するハードウェア的緩和[23]。

- ゼロレイテンシメモリミラーリングの最適化 (文書化されていない)[24]。

- TAGE分岐予測の導入

- Opキャッシュを4096エントリへ増量

- AGUパイプラインの追加

- チップレットへの最適化

カスタムAPUの採用製品

[編集]- Xbox Series X/S

- PlayStation 5

- Steam Deck

- AMD 4700S

ギャラリー

[編集]-

AMD Ryzen 7 3700X

-

CPUパッケージから取り外されたメインストリームRyzen I/Oダイ

-

EPYC I/Oダイ

-

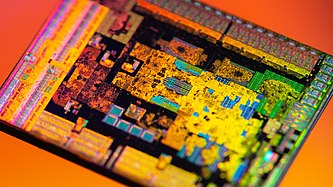

プロセッサパッケージから取り外されたCCD

-

キャリアなしのAMD EPYC 7702サーバ向けプロセッサ

-

殻割りしたAMD EPYC 7702。CCDが8つあることが分かる。はんだTIM (サーマル・インターフェース・マテリアル) が使用されている。Threadripperプロセッサも同様の構造をしている[25]。

関連項目

[編集]参考文献

[編集]- ^ Larabel, Michael (16 May 2017). “AMD Talks Up Vega Frontier Edition, Epyc, Zen 2, ThreadRipper”. Phoronix 16 May 2017閲覧。

- ^ a b Cutress, Ian (20 June 2017). “AMD EPYC Launch Event Live Blog”. AnandTech 21 June 2017閲覧。

- ^ a b Cutress, Ian (9 January 2019). “AMD Ryzen third Gen 'Matisse' Coming Mid 2019: Eight Core Zen 2 with PCIe 4.0 on Desktop”. AnandTech 15 January 2019閲覧。

- ^ online, heise. “AMD Ryzen 3000: 12-Kernprozessoren für den Mainstream”. c't Magazin. 2020年11月6日閲覧。

- ^ a b Leather, Antony. “AMD Ryzen 9 3900X and Ryzen 7 3700X Review: Old Ryzen Owners Look Away Now” (英語). Forbes. 2019年9月19日閲覧。

- ^ “AMD Ryzen 3000 CPUs launching July 7 with up to 12 cores” (英語). PCGamesN. 2019年5月28日閲覧。

- ^ “2nd Gen AMD EPYC™ Processors Set New Standard for the Modern Datacenter with Record-Breaking Performance and Significant TCO Savings”. AMD (7 August 2019). 8 August 2019閲覧。

- ^ Hachman, Mark (9 January 2019). “AMD's CEO Lisa Su confirms ray tracing GPU development, hints at more 3rd-gen Ryzen cores” 15 January 2019閲覧。

- ^ Curtress, Ian (26 May 2019). “AMD Ryzen 3000 Announced: Five CPUs, 12 Cores for $499, Up to 4.6 GHz, PCIe 4.0, Coming 7/7” 3 July 2019閲覧。

- ^ Thomas, Bill (10 June 2019). “AMD announces the Ryzen 9 3950X, a 16-core mainstream processor” 3 July 2019閲覧。

- ^ Alcorn, Paul (31 January 2018). “AMD Predicts Double-Digit Revenue Growth In 2018, Ramps Up GPU Production”. Tom's Hardware 31 January 2018閲覧。

- ^ Shilov, Anton (6 November 2018). “AMD Unveils 'Chiplet' Design Approach: 7nm Zen 2 Cores Meet 14 nm I/O Die”

- ^ “AMD Unveils 'Chiplet' Design Approach: 7nm Zen 2 Cores Meet 14 nm I/O Die”. AnandTech (6 November 2018). 17 June 2019閲覧。

- ^ a b c “AMD Zen 2 Microarchitecture Analysis: Ryzen 3000 and EPYC Rome”. AnandTech. p. 1 (10 June 2019). 17 June 2019閲覧。

- ^ “AMD Rome Second Generation EPYC Review: 2x 64-core Benchmarked”. AnandTech (7 August 2019). 29 September 2019閲覧。

- ^ https://www.tomshardware.com/reviews/ryzen-9-3900x-7-3700x-review,6214.html

- ^ “AMD Zen 2 Microarchitecture Analysis: Ryzen 3000 and EPYC Rome”. AnandTech (10 June 2019). 17 June 2019閲覧。

- ^ “AMD Zen 2 Microarchitecture Analysis: Ryzen 3000 and EPYC Rome”. AnandTech (10 June 2019). 17 June 2019閲覧。

- ^ https://fuse.wikichip.org/news/1497/vlsi-2018-globalfoundries-12nm-leading-performance-12lp/

- ^ “AMD Ryzen Threadripper 3970X Is An Absolutely Efficient Monster CPU”. 2020年11月6日閲覧。

- ^ “AMD Zen 2 CPUs Come With A Few New Instructions - At Least WBNOINVD, CLWB, RDPID - Phoronix”. 2020年11月6日閲覧。

- ^ “GNU Binutils Adds Bits For AMD Zen 2's RDPRU + MCOMMIT Instructions - Phoronix”. www.phoronix.com. 2020年11月6日閲覧。

- ^ btarunr (12 June 2019). “AMD Zen 2 has Hardware Mitigation for Spectre V4” 18 October 2019閲覧。

- ^ “Surprising new feature in AMD Ryzen 3000”. Agner's CPU blog. 2020年11月6日閲覧。

- ^ https://wccftech.com/amd-ryzen-threadripper-3970x-3960x-delidding-direct-die-cooling-tested/

![殻割りしたAMD EPYC 7702。CCDが8つあることが分かる。はんだTIM (サーマル・インターフェース・マテリアル) が使用されている。Threadripperプロセッサも同様の構造をしている[25]。](http://upload.wikimedia.org/wikipedia/commons/thumb/0/0c/AMD%407nm%2812nmIOD%29%40Zen2%40Rome%40EPYC_7702_ES%402S1404E2VJUG5_BB_ES_DSCx3.jpg/241px-AMD%407nm%2812nmIOD%29%40Zen2%40Rome%40EPYC_7702_ES%402S1404E2VJUG5_BB_ES_DSCx3.jpg)