集積回路

集積回路(しゅうせきかいろ、英: integrated circuit, IC)は、半導体の表面に、微細かつ複雑な電子回路を形成した上でパッケージに封入した電子部品である。

集積回路は、シリコン単結晶などに代表される「半導体チップ」[注釈 1]の表面に、不純物を拡散させることによって、トランジスタ・コンデンサ・抵抗器として動作する構造を形成したり、アルミ蒸着とエッチングによって配線を形成したりすることにより電子回路が作り込まれている電子部品である[注釈 2]。

多くの場合、複数の端子を持つ比較的小型の[注釈 3]パッケージに封入されており、パッケージ内部で端子からチップに配線され、モールドされた状態で出荷され、半導体部品(電子部品)として流通している。

1940年代末のトランジスタの発明に次いで1950年代に考案され、製造技術、微細化技術の進歩により内蔵される部品数がムーアの法則で増え続け、性能が向上し続けている。(→#歴史)

製造工程はフォトリソグラフィという光学技術を利用し、微細な素子や配線をひとつずつ組み立てることなく大量生産できるため(→#製造工程)、現在のコンピュータや電子機器を支える主要な技術の一つとなっている。

歴史

[編集]集積回路の誕生

[編集]実際に集積回路を考案したのは、レーダー科学者ジェフリー・ダマー(1909年生まれ)であった。彼はイギリス国防省の王立レーダー施設で働き、1952年5月7日ワシントンD.C.でそのアイデアを公表した。しかし、ダマーは1956年、そのような回路を作ることに失敗した。各企業は集積回路の実現を目指して、RCAのマイクロモジュール、ウェスティングハウス・エレクトリックのモレキュラーエレクトロニクス、テキサス・インスツルメンツのソリッドステートサーキットが開発された[1]。

初期の集積回路の概念は、モノリシックICというより後のハイブリッドICに近いもので、この概念にしたがって、基板に真空蒸着で抵抗素子やコンデンサを形成してトランジスタと組み合わせる薄膜集積回路や、現在のプリンテッドエレクトロニクスに相当する印刷技術により抵抗や配線、コンデンサなどを1枚のセラミック基板上に集積した厚膜集積回路が開発されていった[1]。

また、1958年にはウェスティングハウスから「Molectronics」という名称の集積回路の概念が発表され[2]、1960年2月にSemiconductor Product誌に掲載された記事に触発されて、電気試験所でも同年12月に、見方次第ではマルチチップ構造のハイブリッドICともいえる、ゲルマニウムのペレット3個を約1cm角の樹脂容器に平行に配列した集積回路の試作に成功した[3][4]。

1961年2月には、ウェスティングハウスと技術提携した三菱電機から、11種類のモレクトロンが発表された[1]。日本で最初のモノリシック集積回路は、東京大学と日本電気 (NEC) の共同開発とされる[5]。

著名な集積回路の特許は、アメリカ合衆国の別々の2つの企業の、2人の研究者による異なった発明にそれぞれ発行された。テキサス・インスツルメンツのジャック・キルビーの特許「Miniaturized electronic circuits」は1959年2月に出願され、1964年6月に特許となった (アメリカ合衆国特許第 3,138,743号)。フェアチャイルドセミコンダクターのロバート・ノイスの特許「Semiconductor device-and-lead structure」は1959年7月に出願され、1961年4月に特許となった(アメリカ合衆国特許第 2,981,877号)。しかし、「キルビー特許紛争」などと呼ばれるように(ちなみに「キルビー特許」に対し、ノイスの特許は「プレーナー特許」と呼ばれることがある)多くの議論を発生させることとなった。

技術的な内容とはほぼ無関係に、業界の権益争いとして、特許優先権委員会においてどちらの特許が「集積回路の特許として有効であるか」を、法的に認定させる争いが勃発した(技術的な判断が目的なのではなく、あくまで「法的にどちらが有効か」を認めさせることが目的である)。キルビーの特許出願から10年10か月を経て決着し、ノイスの勝利が確定した。しかし、そのような法的勝利は、実際にはほとんど意味がなかった。

ライセンスビジネス的には、1966年にテキサス・インスツルメンツとフェアチャイルドセミコンダクターを含む十数社のエレクトロニクス企業が、集積回路のライセンス供与について合意に達していたからであり、技術と法律とビジネスというものについて、教訓的な事例となっている。またさらに日本では、20年の紆余曲折を経て1989年に特許となったことで、莫大な額の請求等を伴う紛争となり「サブマリン特許制度」のタチの悪さを際立たせるという役割を担う結果となった。

キルビーとノイスは後に、ともにアメリカ国家技術賞を受け、全米発明家殿堂入りをした。

SSI・MSI・LSI

[編集]SSI, MSI, LSI というのは、集積する素子の数によってICを分類定義[6]したものである。「MSI IC」のようにも言うものであるが、今日ではほぼ使われない。比較的小規模のものを単にIC、比較的大規模のものを単にLSIとしているが、現在ではICとLSIを同義語として使うことも多い。

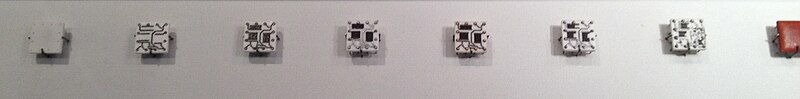

初期の集積回路はごくわずかなトランジスタを集積したものであった。これをSSI (Small Scale Integration) とするのであるが、後にMSI (Middle Scale Integration) やLSI (Large Scale Integration) という語と同時に作られたと思われる、おそらくレトロニムであろう。航空宇宙分野のプロジェクトで珍重され、それによって発展した。ミニットマンミサイルとアポロ計画は慣性航法用計算機として軽量のデジタルコンピュータを必要としていた。アポロ誘導コンピュータは集積回路技術を進化させるのに寄与し、ミニットマンミサイルは量産化技術の向上に寄与した。これらの計画が1960年から1963年まで生産されたICをほぼ全て買い取った。これにより製造技術が向上したために製品価格が40分の1になり、それ以外の需要が生まれてくることになった。

民生品として大量のICの需要を発生させたのは電卓だった。コンピュータ(メインフレーム)でのICの採用は、System/360では単体のトランジスタをモジュールに集積したハイブリッド集積回路(IBMはSLTと呼んだ)にとどまり、モノリシック集積回路の採用はSystem/370からであった。

1960年代に最初の製品があらわれた汎用ロジックICは、やがて多品種が大量に作られるようになり、コンピュータのようにそれらを大量に使用する製品や、あるいは家電など大量生産される機器にも使われるようになっていった。1970年代にはマイクロプロセッサが現れた。

集積度の高いMSIやLSIが普通に生産されるようになると、そのうちそのような分類も曖昧になって、マイクロプロセッサなど比較的複雑なものをLSI、汎用ロジックICなど比較的単純なものをIC、と大雑把に呼び分ける程度の分類となった。

VLSI

[編集]もとの分類ではLSIに全て入るわけだが、1980年代に開発され始めたより大規模な集積回路をVLSI (Very Large Scale Integration) とするようになった。これにより、これまでの多数のICで作られていたコンピュータに匹敵する規模のマイクロプロセッサが製作されるようになった。1986年、最初の1MbitRAMが登場した。これは100万トランジスタを集積したものである。1993年の最初のPentiumには約310万個のトランジスタが集積されている。また、設計のルール化はそれ以前と比較して設計を容易にした。

また、カーバー・ミードとリン・コンウェイの『超LSIシステム入門』[注釈 4]によりVLSIにマッチした設計手法が提案された。これはMead & Conway revolution(en:Mead & Conway revolution)と呼ばれることもあるなどの影響をもたらした。たとえば、1950年代には、大学で最先端のコンピュータを実際に建造するなどといったこともさかんだったわけであるが、1970年頃以降にはコストの点で現実的ではなくなっていた。それが、CAD等の助けによりパターンを設計してチップ化する、という手法で、大学などでも最先端の実際の研究がまた可能になった、といった変化を齎したのが一例である。たとえば初期のRISCとして、IBM 801、バークレイRISC(SPARCへの影響が大きい)、スタンフォード系のMIPSがまず挙がるが、後者2つにはその影響がある。

ULSI

[編集]VLSIに続いて、新たに ULSI (Ultra-Large Scale Integration) という語も作られ、集積される素子数が100万以上とも1000万以上ともされているが、そのような集積度の集積回路も、今日普通はVLSIとしている。

WSI

[編集]WSI (Wafer-Scale Integration) は、複数のコンピュータ・システム等の全体をウェハー上に作り込み、個別のダイに切り離さずにウェハーの大きさのままで使用するという構想である[注釈 5]。現状では、1品もので、コストが非常に高額であっても良いというような特殊な用途・特殊な要求に基づき生産するような装置で採用されている。たとえば、人工衛星や天体観測望遠鏡の光学受像素子では、つなぎ合わせて作ると歪みや隙間が生ずるので、1枚のウェハーの全面を使用した物が作られている。

SoC

[編集]System-on-a-chip (SoC) は、従来別々のダイで構成されていたものを統合することで、独立して動作するシステム全体をひとつの集積回路上に実現するものである。例えば、マイクロプロセッサとメモリ、周辺機器インターフェースなどを1つのチップに集積するものである。

固体撮像素子

[編集]集積回路技術の進歩の一例であるが、以前は撮像管などと呼ばれる真空管だった、映像を撮影する撮像素子も、電荷結合素子 (CCD) の技術開発が進み、固体撮像素子としてCCDイメージセンサが作られ、家庭用ビデオカメラの大幅な小型化などにまず貢献した。続いてCMOSイメージセンサも作られた。やがて静止写真用にも十分な解像度を持つようになり、デジタルカメラが銀塩カメラを一掃した。

伸縮・折り畳み可能なシリコン集積回路

[編集]このシステムは、単結晶硅素の無機の整列アレイを含む無機電子材料と、極薄のプラスチックやエラストマー基板を統合している。[7]

回路設計

[編集]製造工程

[編集](集積回路に限らず)半導体製造は、ウェハー上に素子や回路を形成する前工程と、そこで作られたウェハーをダイに切断し、パッケージに搭載した後に最終検査を行う後工程に大きく二分される。なお、これらの工程は一般に複数の工程専門企業がそれぞれの工場で順次行っていくものである。1社ですべての工程を行うケースはほぼなく、あったとしても非常に稀である。

一般的には、設計・ウェハー製造・表面処理・回路形成・ダイシング・基材製造・ボンディングの各工程に専業企業が存在し、デザイン・ウェハー切り出し・アンダーフィリング・検査が前記から分かれて専業化している場合、加えて各工程で使用される材料・加工にも専業メーカーが存在する。一つの集積回路パッケージが出来上がるまでに関わるメーカーの数は少なくとも5、多いときには30社とも言われる。

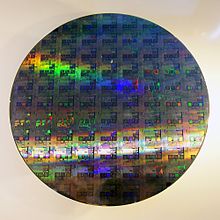

ウェハー製造

[編集]集積回路の母材となるウェハーの原材料は、半導体の性質を持つ物質である。一般的な集積回路ではそのほとんどがシリコンであるが、高周波回路では超高速スイッチングが可能なヒ化ガリウム、低電圧で高速な回路を作りやすいゲルマニウムも利用される。

集積回路の歩留まりとコストは、ウェハーの原材料である単結晶インゴットの純度の高さと結晶欠陥の数、そして直径に大きく左右される。2007年末現在のウェハーの直径は300 mmに達する。インゴットのサイズを引き上げるには、従来の技術だけでは欠陥を低くすることが難しく、多くのメーカーが揃って壁に突き当たった時期があった。シリコン単結晶引き上げ装置のるつぼを超伝導磁石で囲みこみ、溶融したシリコンの対流を強力な磁場で止めることで欠陥の少ない単結晶が製造可能になった。

前工程

[編集]

前工程は、設計者によって作られた回路のレイアウトに従ってウェハー上に集積回路を作り込む工程である。光学技術、精密加工技術、真空技術、統計工学、プラズマ工学、無人化技術、微細繊維工学、高分子化学、コンピュータ・プログラミング、環境工学など多岐にわたる技術によって構成される。

表面処理

[編集]集積回路は半導体表面に各種表面処理を複数実施して製造される。まずウェハーにはイオン注入によってドープ物質を打ち込み、不純物濃度を高める措置が行われる(最初に作られるこの層がゲートなどの集積回路の中枢となる)。さらにSOIではウェハーに絶縁層を焼きこむか張り合わせることで漏れ電流を押さえ込む処置が行われる。そしてレジスト膜の塗布、ステッパーによる露光、現像処理によるレジスト処理を複数行い、その間に回路構造物の母体となるシリコンの堆積、イオン注入によるドープ物質の注入、ゲートや配線の土台となる絶縁膜の生成、金属スパッタリングによる配線、エッチングによる不要部分の除去などが行われる(フォトリソグラフィ)。集積回路の立体的な複雑さを配線層の枚数で数えることから4層メタル・6層メタル等と表現する。この表面処理技術は現在進行形であり、2014年現在ではHigh-K絶縁膜、添加物打ち込み、メタルゲート、窒化物半導体素子など新たな技術が導入されている。さらに新しい技術は、より微細化したプロセス・ルールと共に世に出ると言われている。

クリーンルーム

[編集]半導体工場の生産ラインは、それ自体が巨大なクリーンルームとなっている。生物学的クリーンルームよりも、半導体製造現場のほうが遥かに清浄度が高い。ウェハー上の1つの細菌細胞は、トランジスタ100個近くを覆い隠す。2008年の先端プロセス・ルールである45nmは、ウイルス以下の大きさである。製造中の半導体は、人間がいる環境ではどこにでもあるナトリウムに大変弱く、それが絶縁膜に浸透するため、特にCMOSトランジスタには致命的欠陥になる。

半導体工場のクリーンルーム内に導入される空気は、部屋や場所ごとに設定されたクリーン度に応じて、何度もHEPAフィルターやULPAフィルターで、空中微粒子を濾しとられたものが使われる。また水はイオン交換樹脂とフィルターによって、空気同様に水中微粒子を徹底的に除去された超純水を使用している。

大量のナトリウムを含み、皮膚から大量の角質細胞の破片を落下させ、振動をもたらすヒトは、半導体プロセスにとって害をなす以外の何物でもなく、クリーンスーツ、いわゆる“宇宙服”を着て、製造ラインを汚染しないようにしている。もっとも工場は高度に自動化されており、人間が製造ラインに出向くのは、機械の故障といったトラブルがあった時だけである。

ウェハーテスト

[編集]ウェハー上への回路形成が完了したら、半導体試験装置を用いて回路が正常に機能するかを確認するウェハーテストを行う。半導体の動作特性は温度にも左右されるため、常温に加え高温や低温下での試験も行われる。

ウェハーテストの結果はダイにマーキングされ、後述する後工程では良品とマークされたダイのみが組み立て対象となる。

欠陥救済

[編集]ダイ面積の大きい超大規模集積回路では、チップ上に一つも欠陥がない完璧な製品を作ることは非常に難しい。そこで、設計段階で予備の回路を前もって追加し、ウェハーテストで不良が検出されたときにそこを予備回路で補うことで歩留まりを上げる救済が行われる。回路の切り替えは、回路上に形成されたヒューズを、レーザーまたはウェハーテスト中に電流を流して切断することで実現している。

DRAMやフラッシュメモリでは、製品で決められた容量に加え予備のメモリ領域を用意しておき、不良箇所をテストで見つけた時点で配線のヒューズを切り予備領域に切り替えることが一般的に行われる。また、CPUでオンダイのコプロセッサや、マルチコアプロセッサの各コアなど、その内部に不良があった場合にはそれを切り離して、ラインナップ中の低グレードの製品とする、あるいは最初から全てが機能することは期待しない、といった手法もある。例えば、Cellプロセッサは

後工程

[編集]

前工程で良品としてマーキングされた回路をウェハーから切り出し、シートに貼り付けてパッケージに搭載する。端子との配線や樹脂で封止し、最終製品の形になる。その後、初期不良をあぶり出すバーンイン試験や製品の機能を確認するファイナルテストを経て出荷される。

ダイシング

[編集]ダイシング工程では、前工程で製造されたウェハーをチップの形に切り離す。ダイシングには、薄い砥石を用いて切断する方法と、レーザーを用いる方法が主流である。

ボンディング

[編集]

チップをパッケージ基板に搭載し、チップ側の端子とパッケージの端子を接続する工程はボンディングと呼ばれる。主なボンディング手法を下に示す。

ワイヤ・ボンディング

[編集]フリップチップボンディング

[編集]- チップ上にバンプと呼ばれる接続用の突起を載せ、その面をパッケージ基板に合わせて接続する方法。チップ全面を接続に使えるため、端子数が多くかつチップ面積が小さい集積回路でよく利用される。

封止

[編集]ボンディングによる配線が完了したら、外部からの衝撃や水分から集積回路を保護する封止を行う。一般的な集積回路では、モールド剤でチップやボンディングワイヤーを保護するための注入成形を行う。集積回路の黒い外見はこの樹脂によるものである。樹脂が固まった後、チップ毎に切り離せば集積回路は完成する。近年のCPUやGPU、液晶ドライバICなどの超精密集積回路にはモールド剤を用いず、アンダーフィルと呼ばれる一液硬化の樹脂を用いる。ボンディングの後、基材とIC間に注入を行いキュア炉と呼ばれる装置でリフローし、硬化させる。

バーンイン

[編集]

集積回路の故障率は一般的にバスタブカーブと呼ばれる確率分布に従う。バスタブカーブでは、使用開始直後に高い不良率を示す初期不良期間を経て、低い不良率を維持する偶発故障期間に移行する。劣化を加速する条件下で短時間集積回路を動作させることでこの初期不良をあぶり出す工程がバーンイン(burn-in、焼入れ。エイジングとも)である。バーンインであぶり出された初期不良は次の品質検査によって取り除かれる。

具体的には、高温下で一定時間集積回路に電流を流すことで劣化を加速している。これは、劣化を化学反応として捉えた場合、劣化速度と温度はアレニウスの式の関係に従うとの考え方によるものである。

品質検査

[編集]最後に、集積回路が製品として正常に機能するかを確認する検査を行う。封止樹脂に欠けやひび、リードフレームやBGAパッケージのボール端子に異常が無いかを確認する外観検査、ボンディングによる電気接続が確実に行われ、チップが完全に動作するかを半導体検査装置で確認する電気検査が行われる。

プログラム書き込み

[編集]EEPROMやフラッシュメモリなどの記憶素子を混載した製品では、プログラムをそれらに書き込む作業も行われる。プログラムの内容を切り替えることで、同一のマスクから異なるグレードや入出端子の異なる集積回路を作り出すことができる。またCPU等の製品で、実際に動作可能な最高速度に応じたクロック倍率を後処理で設定することで、グレードの異なる製品を同一生産ラインから製造している。

プロセス・ルール

[編集]プロセス・ルールとは、集積回路をウェハーに製造するプロセス条件をいい、最小加工寸法を用いて表す。プロセス・ルールによって、回路設計での素子や配線の寸法を規定するデザイン・ルールが決まる。

通常、最小加工寸法はゲート配線の幅または間隔である。ゲート配線幅が狭くできれば、金属酸化物電界効果トランジスタ (MOSFET) のゲート長が短くなるから、ソースとドレインの間隔が短くなり、チャネル抵抗が小さくなる。したがって、トランジスタの駆動電流が大きくなり、高速動作が期待できる。このため、プロセス・ルールは、高速化を期待して、ゲート長のことを指す場合もある。特にDRAMプロセスでは、ゲート長はゲート配線の最小寸法を使わない場合があるし、拡散層とメタル層を導通させるコンタクトの径が最小加工寸法の場合もある。つまり、プロセス・ルールは、製造上の技術的な高度さや困難さを示す指標と言える。

プロセス・ルールが半分になれば、ダイの外部配線部を除けば、同じ面積に4倍のトランジスタや配線が配置できるため、同じトランジスタ数では4-1倍 (4分の1) の面積になる。ダイ面積が4分の1に縮小できれば1枚のウェハーから取れるダイが4倍になるだけでなく、歩留まりが改善されるためさらに多くのダイが取れる。トランジスタ素子が小さくなればMOSFETのチャネル長が短くなり、ON/OFFの閾値の電圧 (Vth) を下げられ、低電圧で高速のスイッチング動作が可能となるため、リーク電流の問題を考えなければ、消費電力を下げながら性能が向上する。

伝播遅延は次の式に表される関係に従う。

-

- : 伝播遅延

- : 負荷容量

- : 電源電圧

- : ゲート酸化膜厚

- L : ゲート長

- W : ゲート幅

- : キャリア移動度

- : ゲート酸化膜誘電率

- : しきい値電圧[8]

プロセス・ルールは、フォトマスクからウェハーに回路を転写する半導体露光装置の光学分解能や、エッチング工程の寸法変換差の改善などで更新されてきた。プロセス・ルールの将来予測は、ムーアの法則を引用されることが多い。

半導体露光装置は非常に高い工作精度が要求され、製造の大部分が人間の手作業で行われる。ウェハーを載せるスライドテーブルは、高い水平度を実現するために非常にキメの細かい砥石で職人が磨いたレールの上に乗せられる。微細パターンをウェハー上に転写する光学系には、原子単位で表面の曲率が修正されている超高精度なレンズが用いられている。

微細化

[編集]半導体露光装置メーカーは1社か2社の最先端半導体メーカーと共同で次の世代や次々世代の半導体露光装置を開発し、まずその半導体メーカーに向けて製造する。その開発によって生み出された装置を、2 - 3年程度後に最先端に続く半導体メーカーが量産のために購入する頃には最先端半導体メーカーはその先の世代の試験運用をはじめる。この循環があるために演算プロセッサのプロセスルールは、350 nm/250 nm/180 nm/130 nm/90 nm/65 nm/45 nm/32 nm/22 nm/14 nm/10 nm といった飛びとびの値になるのが普通である。最先端のプロセス・ルールは2020年時点で5nmに達していて[9]、3 nm, 2 nmと微細化が進んで行くと予想されている[10][11][12]。一方DRAMやフラッシュメモリのような記憶用半導体では小刻みにプロセスルールを縮小している。DRAMにおける一般的なプロセス・ルールは2007年には65nm、2008年には57 nmと縮小を行い、2013年には32 nmを想定している。これは、製品の急激な低価格化によって各メーカーが新規投資を控え、既存設備の改善によって生産性を向上させることが狙いである[13]。ただし最先端の微細化が要求される携帯端末向けなどには、2010年時点で25nmの製品が、2020年時点で10 nmの製品が投入されている[14]。

- 2015年、2016年第5世代と第6世代のIntel Coreを14 nmで製造している。2016年中に10 nmを実用化(実際には2019年[15])、2017年には7 nm(実際には2023年予定[16])へ[17]。

- 2015年7月、IBMは7 nmプロセスの試作品を発表[18]、一桁ナノプロセスの時代を迎える。

- 2016年3月、インテルはXeon E5-2600 v4 CPU、14 nm、22コア/44スレッドを発売[19]。

- 2016年3月、サムスンは18 nmといわれるDRAMを出荷。

- 2020年9月、TSMCの5 nmプロセスによるApple A14が出荷される[20]。

微細化によってプロセスルールが使われる光源の波長よりも短くなると、光の回折や干渉によってマスクの形とウェハー上に作られる像の食い違いが大きくなり、設計通りの回路が形成できなくなる。この問題を解決するため、回路設計にあらかじめこれらの光学効果を織り込んでおく光学近接効果補正が130 nm以下のルールで行われるようになった。光学近接効果補正は、EDAによる自動化が普及している。

2020年頃には、5nmに到達し、CMOSを使った微細化の限界が訪れるとの推測されており、新しい素材・構造の研究や微細化に頼らない手段による集積度の向上も模索されている[21]。

また携帯電話の小型カメラ撮像素子ではフットプリントの都合上、非常に微細化したイメージセンサーを使う。しかし、このセンサーの画素密度は可視光波長では従来のカラーフィルタ方式がまったく役に立たなくなる。このため、メタル層で光を回折させて分光を行ったり、窒化物半導体素子を使って分光することにより、プロセスルールよりも遥かに長い可視光をフォトダイオードに導く。APS-Cサイズで2000万画素を超えるものも同様である[22]。

歩留まり

[編集]歩留まりとは、ウェハーから取れる全てのダイに対する良品ダイの割合を指し、イールド・レート (yield rate) とも呼ばれる。PC用のCPUのように、同じ生産ラインで同じ製造工程を経た製品を、完成製品に後からテストによってグレード(動作周波数)を割り振ることがあるので、グレードを下げれば(低クロックでしか動作させられないCPUでも良品と見なせるため)歩留まりが上がるという結果になる。

半導体故障解析

[編集]半導体故障解析とは、極めて多くの素子の集合体である集積回路に於いて、何処が、どの様に、壊れているのかを解析する技術である。LSIテスタ(半導体試験装置)では、不良品であることは分かっても、その回路の何処に異常があるのかまでは分からない。数千万ものトランジスタが集積された回路に於いて、その一つ一つを試験していくのは現実的ではなく、また、それ以上に配線の不良などもあり得る。従って、集積回路の登場当初から、集積度の向上に伴って、故障解析技術も進歩している。

分類

[編集]構成

[編集]モノリシック集積回路

[編集]

モノリシック集積回路は1片のチップに、トランジスタ、ダイオード、抵抗器などの回路素子を形成し、素子間をアルミニウムなどの蒸着によって配線した後、数mm - 十数mm角の小片に切り出したものである。組み立て工数が少ないため安価である。

シリコン(Si、珪素)単結晶基板上に平面状に構成するトランジスタ(プレーナ型トランジスタ)を発展させたものである。アナログICとデジタルICのどちらも1960年代から発展が始まっているが、1990年代には製造プロセスの進歩により高度なアナログ・デジタル混在回路も見られるようになった。

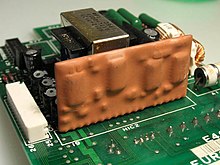

ハイブリッド集積回路

[編集]

比較的小さいプリント基板に、多数の個別部品や複数のチップ(マルチチップモジュール)などを直接、高密度さらには立体的に実装・配線し、さらにモールドするなどして一体の部品としたものである。

制御回路が一体化された大電力の増幅回路やスイッチング回路(インテリジェントパワーモジュール)や、高密度実装が要求される携帯機器・自動車・航空機・軍事用、集積回路同士の距離が演算速度に影響を与えるスーパー・コンピュータやメインフレーム・コンピュータなどに用いられる。メインフレームコンピュータやスーパーコンピュータで使われるマルチチップモジュールは100層を超えるセラミック基板を焼結生成した非常に高度な立体回路を構成している。プリント基板においてもビルドアップと呼ばれる、複数の多層基板を貼り合わせて回路を構成する技術が開発されているため、ハイブリッド集積回路の多層化製品とプリント基板の多層化製品の境目は無くなっている。

パッケージ

[編集]機能別分類

[編集]ASIC、システムLSI(特定用途向け IC・LSI)

[編集]- 音声合成LSI

- LCDドライバ

ASSP

[編集]デジタル制御用LSI

[編集]汎用メモリ

[編集]専用メモリ

[編集]アナログ集積回路

[編集]- オペアンプ(演算増幅器)

- アナログ-デジタル変換回路

- デジタル-アナログ変換回路

- 電源回路

- パワーアンプ - ドライバ

- 音響用アンプ回路

- 液晶ディスプレイドライバ

- モータドライバ

- RF回路

- 映像信号処理 - NTSC信号処理

- タイミング回路 - PLL - VCO

- 半導体センサ

- CMOSイメージセンサ

- CCDイメージセンサ

- 温度センサ

- 圧力センサ

- 加速度センサ

- 半導体リレー

複合製品

[編集]セキュリティチップ

[編集]この節の加筆が望まれています。 |

コンピューターに耐タンパー性能を与えるためのSystem-on-a-chipモジュール。I/Oポートと電源端子のみを備え、マイクロコントローラーとして全てのロジックをワンチップに収納してある。鍵管理・鍵ブロックの登録と払い出し・Worm機能などが盛り込まれ、中間者攻撃やサイドチャネル攻撃からコンピューターシステムを防御する。世界で最も多く使われているセキュリティチップがICカードである。システム防衛の要として使われるが、通常スタンドアロンで動作する物は無い。バックエンドシステムにデータベースを備え、そのデータベースにアクセスする鍵が格納される(過去に実データを格納するICカードもあったが耐タンパー性の悪さから、B-CASカード等限定受信システム以外は撤退している。日本、EUではカードが解析・改ざんされ限定受信システムが崩壊した)。おサイフケータイ・Suicaなどで知られるワイヤレス電子マネー・電子発券システムもセキュリティチップである。このシェアはソニーが開発したFelicaが主流であり、NFCとしてISOで標準化された。携帯電話のSIMカードもセキュリティチップである。Microsoft WindowsはWindows Vistaから、セキュリティチップの本格採用を始めた。セキュリティチップに電子証明書を格納し、ハードディスクを暗号化する。それ以前は電子署名ベースのEFSを搭載していたが、ユーザープロファイルの消滅がユーザー証明書の喪失につながりデータを損失する事故があった。またシステム全体を暗号化することができなかった。インテルはvProとしてWindows NTにセキュリティチップをオプションで採用した暗号化システムを提供していた。しかし一般ユーザーには利用されず、主にITプロフェッショナルが運用する大規模システムでつかわれた。

耐タンパー性技術は日々進歩しており、長い鍵を処理できる高性能プロセッサの搭載、光消去EPROMによるチップ取り出しの困難化(チップに光を当てるとフローティングゲートから電荷が流出してデータが消滅する)など改良が重ねられている。

脚注

[編集]注釈

[編集]出典

[編集]- ^ a b c 1960年代初 国産ICのスタート

- ^ 城阪俊吉、私とハイブリッドマイクロエレクトロニクスの出会い -戦後40年のやきもの 『HYBRIDS.』 1988年 4巻 1号 p.2-20, doi:10.5104/jiep1985.4.2

- ^ 米誌に触発された電試グループ

- ^ 固体回路の一試作 昭和36(1961)年4月8日 電気四学会連合大会

- ^ 東大グループは「固態型論理回路」 半導体産業人協会 日本半導体歴史館 志村資料室 第II部

- ^ The Bipolar Digital Integrated Circuits Data Book, 日本テキサスインスツルメンツ

- ^ Kim, Dae-Hyeong; Ahn, Jong-Hyun; Choi, Won Mook; Kim, Hoon-Sik; Kim, Tae-Ho; Song, Jizhou; Huang, Yonggang Y.; Liu, Zhuangjian et al. (2008-04-25). “Stretchable and Foldable Silicon Integrated Circuits” (英語). Science 320 (5875): 507–511. doi:10.1126/science.1154367. ISSN 0036-8075.

- ^ 福田哲生著 『はじめての半導体シリコン』工業調査会 2006年9月15日初版第1刷発行 ISBN 4769312547

- ^ 株式会社インプレス (2020年1月23日). “TSMC、5nmプロセス「N5」を2020年上半期に立ち上げ 〜6 nmは予定通り年内量産開始の見込み”. PC Watch. 2021年4月8日閲覧。

- ^ 株式会社インプレス (2021年1月18日). “TSMC、3 nmプロセスのリスク生産を2021年内にも開始”. PC Watch. 2021年4月8日閲覧。

- ^ 株式会社インプレス (2019年5月16日). “Samsung、3 nmプロセスで独自のGAAFET構造「MBCFET」採用へ ~6nmは年内、5nmを2020年より量産開始”. PC Watch. 2021年4月8日閲覧。

- ^ 株式会社インプレス (2020年1月30日). “【福田昭のセミコン業界最前線】 2020年も半導体はおもしろい(前編)”. PC Watch. 2021年4月8日閲覧。

- ^ 日経エレクトロニクス 2007年11月5日号「激安DRAMを活かす」 p.63

- ^ 株式会社インプレス (2020年3月26日). “Samsung、業界初のEUV採用DRAMモジュールの出荷開始”. PC Watch. 2021年4月8日閲覧。

- ^ “笠原一輝のユビキタス情報局ː Intel、第10世代Core発表。10nmプロセスで、L1が1.5倍、L2は倍増に”. 2021年4月26日閲覧。 “初期の計画では2017年末の出荷だったが、Kaby Lakeの微細化製品として計画されてきた同じ10nm採用のCannon Lakeがうまく立ち上がらず、結果的に事実上のスキップ(実際にはGPUなし版が細々と出荷されている)になり、2019年にずれ込んでしまうというかたちになってしまった。”

- ^ “笠原一輝のユビキタス情報局ː Intel、2023年の製品計画プランを延期。ゲルシンガー氏の新体制で強いIntelへの回帰なるか”. 2021年4月26日閲覧。 “Intelの次の製造技術であり、TSMCの5 nmと同程度の性能を持っているとされる7 nmの製造計画は2022年に開始され、量産は2023年になると見られている。”

- ^ インテルCPUロードマップ 2016年中に10nmプロセスを量産、7nmは2019年 ASCIIデジタル2016年04月18日

- ^ ついに“ひと桁”、7 nmプロセス開発へ加速 EE Times Japan Weekly 2016年03月28日

- ^ “Broadwell-EP”こと「Xeon E5-2600 v4」が販売開始 ASCII 2016年04月01日

- ^ ASCII. “アップル異例の「順番入れ替わり」、それでも「プロセッサー自前開発」で強みを見せる (1/2)”. ASCII.jp. 2021年4月8日閲覧。

- ^ New nano logic devices for the 2020 time frames

- ^ マイクロ分光素子を用いたイメージセンサの高感度化技術を開発 Panasonic Newsroom プレスリリース 2013年2月4日

参考文献

[編集]- 電子立国日本の自叙伝 - ビデオ、レーザーディスク、DVD、および単行本がある。

- カーバー・ミード、リン・コンウェイ 『超LSIシステム入門』菅野卓雄, 榊裕之監訳。培風館。 1981年。ISBN 4-563-03179-8

- 電子情報技術産業協会 電子デバイス部 半導体技術グループ 編『ICガイドブック —2006年版— 生活を豊かに、社会を支える半導体』日経BP、2006年。ISBN 4-86130-156-4。

- 泰司増樹 『CMOSアナログ/デジタルIC設計の基礎』