PMOSロジック

PMOS または pMOSロジック(Metal-Oxide-Semiconductor : 金属-酸化物-半導体が由来)は、pチャネルエンハンスメントモードMOSFETに基づいたデジタル回路のファミリである。 1960年代後半から1970年代初頭において、NMOSロジックやCMOSロジックに置き換えられるまでPMOSロジックは、大規模集積回路 (LSI)のための支配的な半導体技術であった。

歴史と応用

[編集]モハメド・アタラとダウォン・カーンは、1959年にベル研究所で最初に動作したMOSFETを製造した[1]。 彼らは、PMOSデバイスとNMOSデバイスの両方を製造したが、PMOSだけが動作した[2]。 製造工程における汚染物質(特にナトリウム)が実用的なNMOSデバイスを製造するために十分に管理されるようになるまで10年以上かかったからであった。

バイポーラトランジスタ(当時、集積回路で利用できる唯一のPMOS以外のデバイス)と比べて、MOSFETは多くの利点があった。

- 同精度の半導体デバイス製造技術を仮定すると、一つのMOSFETは一つのバイポーラトランジスタの面積の10%だけを必要とする[3](pp87)。その主な理由は、MOSFETが自己絶縁であり、同じチップ上の隣の部品と絶縁するためにpn接合分離を必要としないからである。

- MOSFETは、より少ない工程で作ることができた。それゆえにより単純により安く製造することができる(MOSFETは1回だけの拡散ドーピングだけで製造できた[3](pp87)が、バイポーラトランジスタは4回必要だった[3](pp50))。

- MOSFETの場合、静止時に流れるゲート電流はないので、MOSFETで作られた集積回路の消費電力を低くすることができる。

バイポーラトランジスタを使った集積回路と比べて欠点もあった。

ジェネラル・マイクロエレクトロニクスは、1964年に最初の商用PMOS回路を導入した。120個のMOSFETでできた20ビットシフトレジスタであり、当時としては信じられないほどの集積度であった[5]。 1965年にジェネラル・マイクロエレクトロニクスは、ビクター・コンプトメーター(ビクター・テクノロジー)という電子計算機のために23個のカスタム集積回路を開発したが[5]、当時のPMOS回路の信頼性からするとあまりにも野心的で結局のところジェネラル・マイクロエレクトロニクスは消滅することになった[6]。 他の会社は、大きなシフトレジスタ(ジェネラル・インストゥルメント)[7]、あるいはアナログマルチプレクサ3705(フェアチャイルドセミコンダクター)[8]のようなPMOS回路を製造し続けた。それらは当時のバイポーラトランジスタでは実現不可能であった。

1968年にポリシリコン自己整合ゲート技術という大きな技術革新が登場した[9]。 フェアチャイルドセミコンダクターのトム・クレインとフェデリコ・ファジンは、商業的に実用化できるように自己整合ゲートを改良した。その結果、最初のシリコンゲート回路としてアナログマルチプレクサ3708を市場に出すことになった[9]。 自己整合ゲートプロセスは、製造時の許容誤差を小さくし、MOSFETをより小さくし、ゲート容量を縮小した。 例えば、PMOSメモリにこの技術を適用すると、3倍から5倍の速度になり、チップに占める面積は半分になった[9]。 ポリシリコンゲート材料は、自己整合ゲートを可能にしただけではなく、スレッシュホールド電圧を低下させた。その結果として最小電源電圧を低くすることになった(例えば、-16 V[10](p1-13))。消費電力を削減することにもなった。 電源電圧が低くなったので、ポリシリコン自己整合ゲートPMOSロジックは、「低電圧PMOS」と呼ばれ、それと対照的に古いものは「高電圧PMOS」と呼ばれるようになった[3](pp89)。

様々な理由からフェアチャイルドセミコンダクターは、PMOSに関係する管理職が望むほど集中的にPMOS集積回路の開発を進めなかった[11](pp1302)。 それら管理職の中の二人であるゴードン・ムーアとロバート・ノイスは、1968年にその代わりとしてインテルを起業することを決めた。 すぐに彼らは、フェアチャイルドの他の技術者と合流した。その中にフェデリコ・ファジンとレスリー・L・ヴァダスもいた。 1969年にインテルは、最初のPMOSロジックを使った容量256ビットのStatic Random Access Memory (SRAM)であるIntel 1101を発表した[11](pp1303)。 それに続いて、1970年に1024ビットのDynamic Random Access Memory (DRAM)であるIntel 1103を発表した[12]。 1103は、商業的に成功し、コンピューターの磁気コアメモリを急速に置き換え始めた[12]。 インテルは、1971年に最初のPMOSマイクロプロセッサであるIntel 4004を発表した。 多くの企業がインテルの行動に続いた。 ほとんどの初期のマイクロプロセッサは、PMOS技術で製造された(en:Microprocessor chronologyも参照)。 インテルの4040と8008。 ナショナル・セミコンダクタのIMP-16、PACE、そしてSC/MP。 テキサス・インスツルメンツのTMS1000。 ロックウェル・インターナショナルのPPS-4[13]とPPS-8[14]がPMOSで製造された。 これらのマイクロプロセッサの中にいくつかの商業的に最初のものが存在する。 最初の4ビットマイクロプロセッサ (4004)、最初の8ビットマイクロプロセッサ (8008)、最初のシングルチップ16ビットマイクロプロセッサ (PACE)、そして最初のシングルチップ4ビットマイクロコントローラ (TMS1000。同じチップにCPU、RAM、そしてROMを統合)である[注釈 1]。

1972年までにNMOS技術がついに商業製品に使用できる程度に開発が進んだ。 インテル(Intel 2102)[15]とIBM[12]は、1Kビットメモリチップを発表した。 NMOS MOSFETのn型チャネル内の電子移動度は、PMOS MOSFETのp型チャネル内の正孔移動度の約3倍なので、NMOSロジックはスイッチング速度の向上を可能とした。 このような理由でNMOSロジックは、PMOSロジックを急速に置き換え始めた。 1970年代後半までにNMOSマイクロプロセッサは、PMOSのマイクロプロセッサを追い抜いた[16]。 PMOSは低コストかつ比較的高い集積度だったので、単純な電卓や時計のような用途のためにしばらく使われ続けた。 CMOS技術は、PMOSあるいはNMOSの両方よりも劇的に低い消費電力を確実なものとした。 CMOS回路はフランク・ワンラス[17]によって1963年にすでに提案されており、CMOS技術を使った商用の4000シリーズ 汎用ロジックICは、1968年に製造が始まっていたが、当時のCMOSは製造が複雑でPMOSやNMOSよりも集積度が低く、NMOSよりも速度が遅いという状況だった。 1980年代までかかってCMOSは改良され、CMOSはマイクロプロセッサの主流の技術としてNMOSを置き換えることになった。

解説

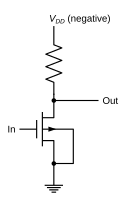

[編集]PMOS回路は、NMOSロジックやCMOSロジックと比較して多くの欠点を抱えていた。複数の異なる電源電圧(正電圧と負電圧の両方)が必要であり、導電状態における消費電力も高かった。 全体的なスイッチング速度も遅かった。 PMOSは、論理回路やその他のデジタル回路を実装するためにpチャネルMOSFETを使っている。 PMOSトランジスタは、n型半導体の中に反転層を作ることによって動作する。 pチャネルとも呼ばれるこの反転層は、p型半導体で作られたソース端子とドレイン端子の間に正孔を導電することができる。

pチャネルは、ゲートと呼ばれる第3の端子に負電圧(-25 Vが一般的だった[18])を印加することによって生じる。 他のMOSFETのようにPMOSトランジスタは、4つの動作領域を持つ。つまり、遮断領域(cut-off/subthreshold)、線形領域(triode)、飽和領域(saturation/active)、そして速度飽和領域(velocity saturation)である[19][20][21]。

PMOSロジックは、設計と製造が容易である(MOSFETは抵抗のように動作させることもできるので、回路全体をPMOS FETで作ることができる)。その一方で、いくつかの欠点がある。 最大の問題は、いわゆる「プルアップネットワーク」(PUN) がアクティブなとき、つまり出力が High のときはいつでもPMOSロジックのゲートを通して直流が流れることである。回路が出力Highのままでアイドル状態になっているときでさえ静的に電力を消費する。

PMOS回路は、HighからLowへ遷移するのも遅い。 LowからHighへ遷移するとき、PMOSのMOSFETは低い抵抗値を示し、出力に容量性電荷が非常に速く蓄積される(非常に低い抵抗を通してコンデンサを充電するのに似ている)。 しかし、出力と負電源の間の抵抗は大きいので、HighからLowへの遷移は、長い時間がかかる(高い抵抗値の抵抗を通してコンデンサを放電するのに似ている)。 低い値の抵抗を使うと、放電を速くすることができるが、出力High時の静的な消費電力は増大する。

それに加えて、非対称な入力ロジックレベルによって、PMOS回路はノイズの影響を受けやすくなる[22]。

ほとんどのPMOS集積回路は、17 Vから24 Vの直流を必要とした[23]。 しかしながら、PMOSで製造されたIntel 4004マイクロプロセッサは、小さい電位差を実現するためにメタルゲートではなくポリシリコンでPMOSロジックを作った。 TTLのロジックレベルと互換性を保つために4004は正電源電圧VSS=+5Vと負電源電圧VDD = -10Vを使用した[24]。

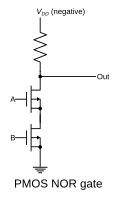

論理ゲート

[編集]p型MOSFETは、論理ゲートの出力と正電源電圧(GND)の間に配置されるいわゆる「プルアップネットワーク(PUN)」になっている。 もしも期待する出力がHigh(GND)ならば、PUNはアクティブになり、正電源(GND)と出力の間に電流の経路ができるようにこの回路は設計されている。

PMOS論理ゲートは、全ての電圧を反転すれば、NMOS論理ゲートと同じ構造になる[25]。 PMOSのNORゲートは、NMOSのNANDゲートと同じ構造であり、逆もまた同様である。 例えば、NORを!(A or B)と表現したとき、入出力を全て反転すると !!(!A or !B)となる。 これをド・モルガンの法則を使って変形すると、!!(!A or !B) = (!A or !B) = !(A and B) なので、NANDになる。

|

|

|

出典

[編集]- ^ “1960: Metal Oxide Semiconductor (MOS) Transistor Demonstrated”. Computer History Museum. 2023年3月4日閲覧。

- ^ Lojek, Bo (2007). History of Semiconductor Engineering. Springer Science & Business Media. pp. 321–323. ISBN 9783540342588

- ^ a b c d Manfred Seifart (1982) (ドイツ語). Digitale Schaltungen und Schaltkreise [Digital Circuits and Integrated Circuits]. Berlin: VEB Verlag Technik. OCLC 923116729

- ^ Mogisters: The New Generation of MOS Monolithic Shift Registers. General Instrument Corp.. (1965)

- ^ a b “1964: First Commercial MOS IC Introduced”. Computer History Museum. 2020年12月7日閲覧。

- ^ “13 Sextillion & Counting: The Long and Winding Road to the Most Frequently Manufactured Human Artifact in History”. Computer History Museum (2018年4月2日). 2020年12月8日閲覧。

- ^ General Instrument MOS Integrated Circuit. General Instrument Microelectronics Division. (September 1966)

- ^ M. J. Robles (1968-04-09). New MOS Multiplex Switch is Bipolar Compatible. Fairchild Semiconductor

- ^ a b c “1968: Silicon Gate Technology Developed for ICs”. Computer History Museum. 2020年12月11日閲覧。

- ^ [1973-08.pdf The Intel Memory Design Handbook]. Intel. (Aug 1973) 2020年12月18日閲覧。

- ^ a b Sah, Chih-Tang (October 1988). “Evolution of the MOS transistor-from conception to VLSI”. Proceedings of the IEEE 76 (10): 1280–1326. doi:10.1109/5.16328. ISSN 0018-9219.

- ^ a b c “1970: MOS dynamic RAM Competes with Magnetic Core Memory on Price”. Computer History Museum. 2020年12月17日閲覧。

- ^ “Rockwell PPS-4”. The Antique Chip Collector's Page. 2020年12月21日閲覧。

- ^ Parallel Processing System (PPS) Microcomputer. Rockwell International. (Oct 1974) 2020年12月21日閲覧。

- ^ “[https://web.archive.org/web/20070809053720/http://download.intel.com/museum/research/arc_collect/timeline/TimelineDateSort7_05.pdf A chronological list of Intel products. The products are sorted by date.]”. Intel museum. Intel Corporation (July 2005). August 9, 2007時点のオリジナルよりアーカイブ。July 31, 2007閲覧。

- ^ Kuhn, Kelin (2018). “CMOS and Beyond CMOS: Scaling Challenges”. High Mobility Materials for CMOS Applications. Woodhead Publishing. p. 1. ISBN 9780081020623

- ^ “1963: Complementary MOS Circuit Configuration is invented”. Computer History Museum. 2021年1月2日閲覧。

- ^ Ken Shirriff (December 2020). “Reverse-engineering an early calculator chip with four-phase logic”. 2020年12月31日閲覧。

- ^ MOSFETの『出力特性』と『線形領域、飽和領域、遮断領域』について! (Electrical Information)

- ^ 速度飽和 Velocity Saturation (sciencompass.com)

- ^ MOS・IC回路設計の基本(2)竹井澄明。線形領域のことを3極管(triode)領域と呼ぶことについて記述されている。

- ^ Khan, Ahmad Shahid (2014). Microwave Engineering: Concepts and Fundamentals. pp. 629. ISBN 9781466591424 2016年4月10日閲覧. "Also, the asymmetric input logic levels make PMOS circuits susceptible to noise."

- ^ Fairchild (January 1983). “CMOS, the Ideal Logic Family”. pp. 6. 2015年1月9日時点のオリジナルよりアーカイブ。2015年7月3日閲覧。 “Most of the more popular P-MOS parts are specified with 17V to 24V power supplies while the maximum power supply voltage for CMOS is 15V.”

- ^ “Intel 4004 datasheet”. pp. 7 (1987年). 16 October 2016時点のオリジナルよりアーカイブ。2011年7月6日閲覧。

- ^ Microelectronic Device Data Handbook (NPC 275-1 ed.). NASA / ARINC Research Corporation. (August 1966). p. 2-51

注釈

[編集]参考文献

[編集]- “What Computers Are Made From”. quadibloc (2018年). 2018年7月2日時点のオリジナルよりアーカイブ。2018年7月16日閲覧。